# PXIe-6943 32 Channel Digital Test Instrument

Publication No. 981052 Rev. A (03-08-2021)

Astronics Test Systems Inc. 4 Goodyear, Irvine, CA 92618 Tel: (877) 388-1952, (949) 859-8999; Fax: (949) 859-7139

https://www.ni.com/en-us/contact-us.html

Copyright 2021 by Astronics Test Systems Inc. Printed in the United States of America. All rights reserved. This book or parts thereof may not be reproduced in any form without written permission of the publisher.

THANK YOU FOR PURCHASING THIS

#### **ASTRONICS TEST SYSTEMS PRODUCT**

For this product, or any other Astronics Test Systems product that incorporates software drivers, you may access our web site to verify and/or download the latest driver versions. The web address for driver downloads is:

http://www.astronicstestsystems.com/support/downloads

If you have any questions about software driver downloads or our privacy policy, please contact us at:

#### atsinfo@astronics.com

#### WARRANTY STATEMENT

All Astronics Test Systems products are designed to exacting standards and manufactured in full compliance to our AS9100 Quality Management System processes.

This warranty does not apply to defects resulting from any modification(s) of any product or part without Astronics Test Systems express written consent, or misuse of any product or part. The warranty also does not apply to fuses, software, non-rechargeable batteries, damage from battery leakage, or problems arising from normal wear, such as mechanical relay life, or failure to follow instructions.

This warranty is in lieu of all other warranties, expressed or implied, including any implied warranty of merchantability or fitness for a particular use. The remedies provided herein are buyer's sole and exclusive remedies.

For the specific terms of your standard warranty, contact Customer Support. Please have the following information available to facilitate service.

- 1. Product serial number

- 2. Product model number

- 3. Your company and contact information

You may contact Customer Support by:

| E-Mail:    | https://www.ni.com/en-us/contact-us.html |       |

|------------|------------------------------------------|-------|

| Telephone: | +1 877 388 1952                          | (USA) |

#### **RETURN OF PRODUCT**

Authorization is required from Astronics Test Systems before you send us your product or sub-assembly for service or calibration. Call or contact Customer Support at 1-877-388-1952 or fax to 1-888-484-4436. We can also be reached at: <u>https://www.ni.com/en-us/contact-us.html</u>.

If the original packing material is unavailable, ship the product or sub-assembly in an ESD shielding bag and use appropriate packing materials to surround and protect the product.

#### **PROPRIETARY NOTICE**

This document and the technical data herein disclosed, are proprietary to Astronics Test Systems, and shall not, without express written permission of Astronics Test Systems, be used in whole or in part to solicit quotations from a competitive source or used for manufacture by anyone other than Astronics Test Systems. The information herein has been developed at private expense, and may only be used for operation and maintenance reference purposes or for purposes of engineering evaluation and incorporation into technical specifications and other documents which specify procurement of products from Astronics Test Systems.

#### TRADEMARKS AND SERVICE MARKS

All trademarks and service marks used in this document are the property of their respective owners.

• Racal Instruments, Talon Instruments, Trig-Tek, ActivATE, Adapt-A-Switch, N-GEN, and PAWS are trademarks of Astronics Test Systems in the United States.

#### DISCLAIMER

Buyer acknowledges and agrees that it is responsible for the operation of the goods purchased and should ensure that they are used properly and in accordance with this document and any other instructions provided by Seller. Astronics Test Systems products are not specifically designed, manufactured or intended to be used as parts, assemblies or components in planning, construction, maintenance or operation of a nuclear facility, or in life support or safety critical applications in which the failure of the Astronics Test Systems product could create a situation where personal injury or death could occur. Should Buyer purchase Astronics Test Systems product for such unintended application, Buyer shall indemnify and hold Astronics Test Systems, its officers, employees, subsidiaries, affiliates and distributors harmless against all claims arising out of a claim for personal injury or death associated with such unintended use.

# FOR YOUR SAFETY

Before undertaking any troubleshooting, maintenance or exploratory procedure, read carefully the **WARNINGS** and **CAUTION** notices.

This equipment contains voltage hazardous to human life and safety, and is capable of inflicting personal injury.

If this instrument is to be powered from the AC line (mains) through an autotransformer, ensure the common connector is connected to the neutral (earth pole) of the power supply.

Before operating the unit, ensure the conductor (green wire) is connected to the ground (earth) conductor of the power outlet. Do not use a two-conductor extension cord or a three-prong/two-prong adapter. This will defeat the protective feature of the third conductor in the power cord.

Maintenance and calibration procedures sometimes call for operation of the unit with power applied and protective covers removed. Read the procedures and heed warnings to avoid "live" circuit points.

Before operating this instrument:

- 1. Ensure the proper fuse is in place for the power source to operate.

- 2. Ensure all other devices connected to or in proximity to this instrument are properly grounded or connected to the protective third-wire earth ground.

If the instrument:

- fails to operate satisfactorily

- shows visible damage

- has been stored under unfavorable conditions

- has sustained stress

Do not operate until performance is checked by qualified personnel.

### **Table of Contents**

| Chapter 1                                      | 1-1 |

|------------------------------------------------|-----|

| Overview and Features                          | 1-1 |

| Introduction                                   | 1-1 |

| I/O Features                                   | 1-3 |

| Front Panel                                    | 1-4 |

| Connectors                                     | 1-4 |

| LED Indicators                                 | 1-4 |

| Digital Board                                  | 1-5 |

| DB Control                                     | 1-5 |

| PCI Express Bridge                             | 1-5 |

| External Timing Bus Control                    | 1-5 |

| Data Sequencer                                 | 1-5 |

| Driver/Receiver Board                          | 1-5 |

| Accessories                                    | 1-5 |

| ETB Links, Cables and Adapters                 | 1-6 |

| ETB Kits                                       | 1-7 |

| Chapter 2                                      | 2-1 |

| Getting Started                                | 2-1 |

| Unpacking and Inspection                       | 2-1 |

| Installing the Module(s) into a PXIe Chassis   | 2-1 |

| Installing the External Timing Bus (ETB) Links | 2-3 |

| Installing the J1 Cable                        | 2-3 |

| Initial Power On                               | 2-4 |

| Software Installation                          | 2-6 |

| VISA Driver                                    | 2-6 |

| Installing the VISA Driver                     | 2-6 |

| C API Instrument Driver                        | 2-7 |

| LabView Instrument Driver                      | 2-7 |

| Low Level VISA Driver                          | 2-8 |

| Chapter 3                                      | 3-1 |

| Hardware Description                           | 3-1 |

| Front Panel                                    | 3-1 |

| J1 Pinout and Signal Description               | 3-2 |

| Mating Cable Pinout                            | 3-3 |

| Digital Board (DB)                             | 3-5 |

| Power                                          | 3-6 |

| PXIe Bridge/32 Bit μP                          | 3-6 |

| Frequency Synthesizer                          | 3-6 |

| Data Sequencer                  |      |

|---------------------------------|------|

| Sequence Logic                  |      |

| Master Clock                    |      |

| System Clock                    |      |

| Test Logic                      |      |

| Record Control                  | 3-8  |

| Trigger Logic                   |      |

| Counter/Timer & Pulse Generator | 3-9  |

| Timing & Waveform Generator     | 3-9  |

| Sequence Controller             | 3-9  |

| Timers                          | 3-9  |

| Probe/Flag RAM                  | 3-9  |

| Pattern RAM                     | 3-9  |

| Record RAM                      | 3-9  |

| Sequence Control                | 3-10 |

| Channel Control                 | 3-10 |

| AUX & Probe Control             | 3-10 |

| DB Monitors                     | 3-10 |

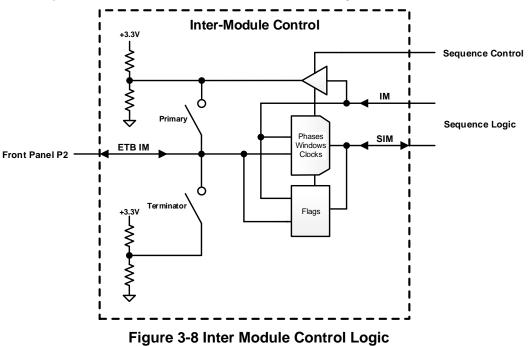

| Inter Module Control            | 3-11 |

| Driver Receiver                 |      |

| Power                           |      |

| DB Bridge/32 Bit µP ADC         |      |

| Channel I/O                     |      |

| Auxiliary I/O                   | 3-12 |

| DR Monitors                     |      |

| Chapter 4                       | 4-1  |

| Programming                     | 4-1  |

| Soft Front Panel                |      |

| Starting the Soft Front Panel   | 4-1  |

| System Panel                    | 4-1  |

| System Panel Menu Bar           | 4-2  |

| File Menu                       | 4-2  |

| File>Exit                       | 4-2  |

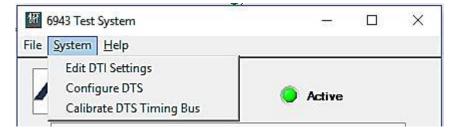

| System Menu                     | 4-3  |

| System>Edit DTI Settings        | 4-3  |

| System>Configure DTS            | 4-3  |

| System>Calibrate DTS Timing Bus | 4-5  |

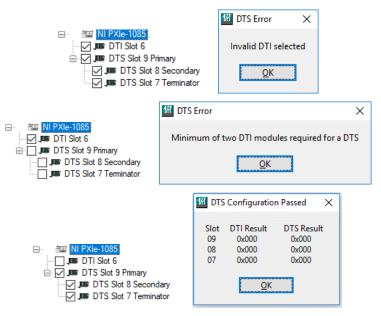

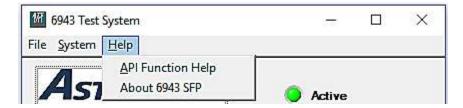

| Help Menu                       | 4-6  |

| Help>API Function Help          | 4-6  |

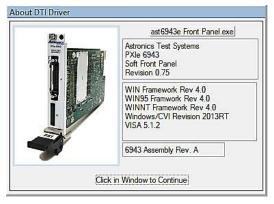

| Help>About 6943 SFP             | 4-6  |

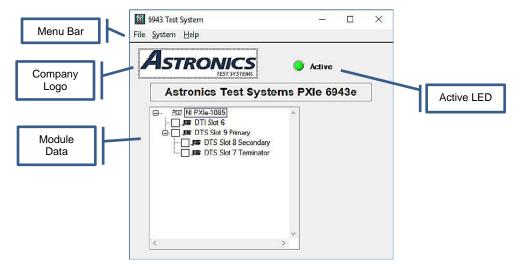

| Company Logo                    | 4-7  |

| Active LED                    | 4-7  |

|-------------------------------|------|

| Module Data                   | 4-7  |

| DTI Main Panel                | 4-7  |

| DTI Main Panel Menu Bar       | 4-8  |

| File Menu                     | 4-9  |

| File>New                      | 4-9  |

| File>Open                     | 4-9  |

| File>Save                     | 4-9  |

| File>Save As                  | 4-9  |

| File>Load Hex File            | 4-9  |

| File>Dump Register Data       | 4-10 |

| File>Set DTI Data             | 4-10 |

| File>Close                    | 4-10 |

| Config Menu                   | 4-10 |

| Config>Module                 | 4-10 |

| Config>Data Sequencer         | 4-10 |

| Config>Channels               | 4-11 |

| Config>Aux Outputs            | 4-11 |

| Config>Interrupts             | 4-11 |

| Edit Menu                     | 4-11 |

| Edit>Data Sequencer           | 4-11 |

| Execute Menu                  | 4-11 |

| Execute>Data Sequencer        | 4-12 |

| Execute>PMU                   | 4-12 |

| Execute>Counter/Timer         | 4-12 |

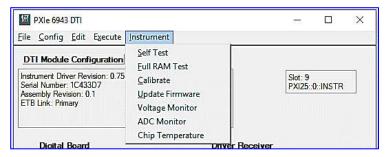

| Instrument Menu               | 4-12 |

| Instrument>Self Test          | 4-12 |

| Instrument>Full RAM Test      | 4-12 |

| Instrument>Calibrate          | 4-13 |

| Instrument>Update Firmware    | 4-13 |

| Instrument>Voltage Monitor    | 4-13 |

| Instrument>ADC Monitor        | 4-13 |

| Instrument>Chip Temperature   | 4-13 |

| Programming Steps             | 4-13 |

| Opening DTI Session(s)        | 4-14 |

| Configuring Hardware Settings | 4-14 |

| Configure Module Panel        | 4-14 |

| Inter-Module Mode             | 4-15 |

| IO Max 116                    | 4-15 |

| IO Max 1732                   | 4-15 |

| Delay Signal                  | 4-15 |

| Delay                             | 4-16 |

|-----------------------------------|------|

| Coarse Delay                      | 4-16 |

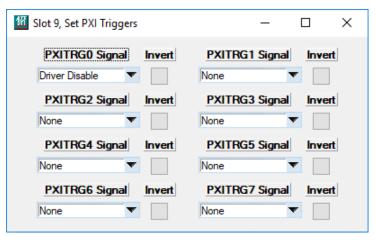

| PXI Triggers                      | 4-16 |

| PXITRGn Signal                    | 4-17 |

| Invert                            | 4-17 |

| D/R Properties                    | 4-17 |

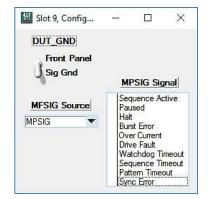

| DUT_GND                           | 4-18 |

| MFSIG Source                      | 4-18 |

| MPSIG Signal                      | 4-18 |

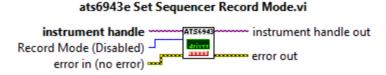

| Sequencer Record Mode             | 4-19 |

| Config Data Sequencer             | 4-19 |

| Configure Clocks                  | 4-20 |

| Master Clock                      | 4-20 |

| System Clock                      | 4-21 |

| External Mode                     | 4-21 |

| External Offset                   | 4-21 |

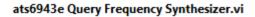

| Synthesizer Freq (MHz)            | 4-22 |

| Synthesizer Ref Source            | 4-22 |

| Reference Freq (MHz)              | 4-22 |

| Configure Timers                  | 4-22 |

| Watchdog Action                   | 4-24 |

| Watchdog Time                     | 4-24 |

| Sequence Timeout State            | 4-25 |

| Sequence Timeout Time             | 4-25 |

| Pattern Timeout                   | 4-25 |

| Pattern Delay 1-2                 | 4-25 |

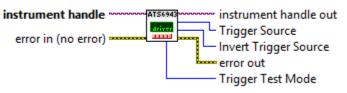

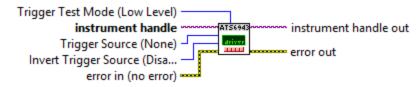

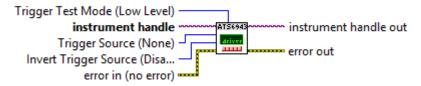

| Configure Triggers                | 4-25 |

| Trigger                           | 4-27 |

| Source                            | 4-27 |

| Test Condition                    | 4-27 |

| Input Mode                        | 4-28 |

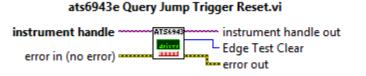

| Edge Test Clear                   | 4-28 |

| Configure Pulse Generator         | 4-29 |

| Mode                              | 4-29 |

| Step                              | 4-30 |

| Period                            | 4-30 |

| Delay                             | 4-30 |

| Width                             | 4-30 |

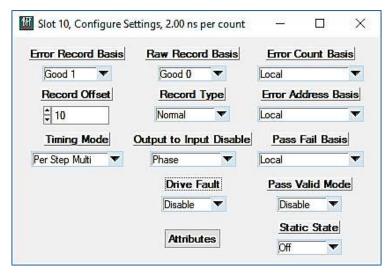

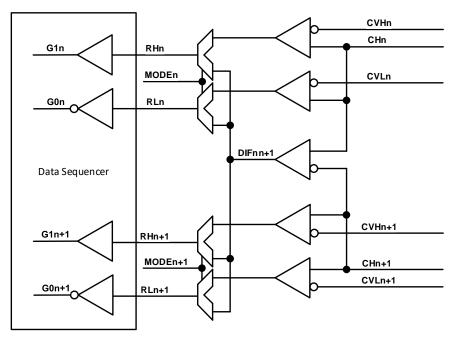

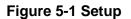

| Configure Data Sequencer Settings | 4-31 |

| Error Record Basis                | 4-31 |

| Raw Record Basis                  | 4-31 |

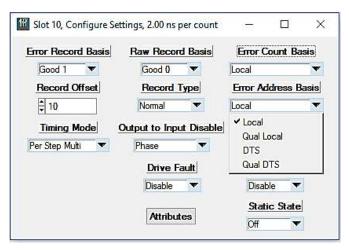

| Record Offset                  | 4-32 |

|--------------------------------|------|

| Record Type                    | 4-32 |

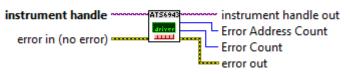

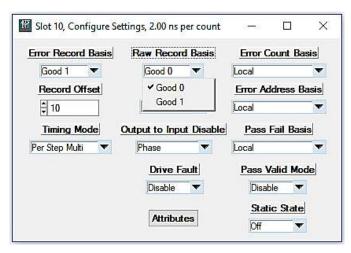

| Error Count Basis              | 4-33 |

| Error Address Basis            | 4-33 |

| Timing Mode                    | 4-34 |

| Output-to-Input Disable        | 4-34 |

| Pass Valid Mode                | 4-35 |

| Drive Fault                    | 4-35 |

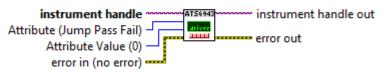

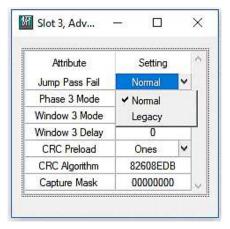

| Attributes                     | 4-35 |

| Jump Pass Fail                 | 4-36 |

| Phase 3 Mode                   | 4-36 |

| Window 3 Mode                  | 4-37 |

| Window 3 Delay                 | 4-37 |

| CRC Preload                    | 4-37 |

| CRC Algorithm and Capture Mask | 4-37 |

| Static State                   | 4-38 |

| Configuring the I/O Channels   | 4-38 |

| Selecting the Channels         | 4-39 |

| Channel Parameters             | 4-39 |

| Channel Function               | 4-40 |

| Stimulus Signal                | 4-40 |

| Stimulus Format                | 4-41 |

| Capture Signal                 | 4-42 |

| Capture Mode                   | 4-42 |

| Static Mode                    | 4-42 |

| Channel Properties             | 4-43 |

| Driver Levels                  | 4-44 |

| Comparator Levels              | 4-44 |

| Driver Slew                    | 4-45 |

| Termination                    | 4-45 |

| Programmable Load Settings     | 4-45 |

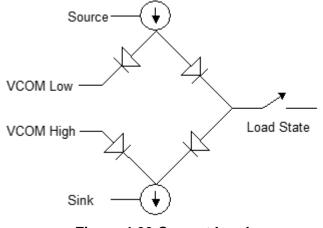

| Load State                     | 4-46 |

| Active Load                    | 4-47 |

| VCOM Sink                      | 4-47 |

| VCOM Source                    | 4-47 |

| Sink Current (mA)              | 4-47 |

| Source Current (mA)            | 4-47 |

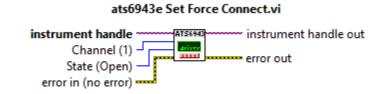

| Channel Connect                | 4-47 |

| Comparator Delay               | 4-48 |

| Channel Mode                   | 4-48 |

| Configuring the AUX Channels   | 4-49 |

| Configuring the AUX Signals  | . 4-50 |

|------------------------------|--------|

| State                        | 4-51   |

| Source                       | 4-51   |

| Input Bus Source             | 4-52   |

| Editing the Data Sequencer   | . 4-53 |

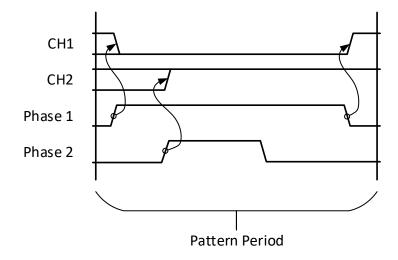

| Editing the Timing Sets      | . 4-53 |

| Timing Set Value Rules       | 4-56   |

| Advanced Timing Set Features | . 4-56 |

| Phase/Window Spanning        | . 4-56 |

| Idle/Standby Timing          | 4-57   |

| Editing the Patterns         | 4-57   |

| Append                       | 4-58   |

| Assign                       | 4-59   |

| Edit Data                    | 4-59   |

| Import/Export Data           | 4-62   |

| Import/Export File Format    | 4-62   |

| Header Format                | 4-62   |

| Data Format                  | 4-63   |

| ASCII Hex                    | 4-63   |

| Binary                       | 4-64   |

| ASCII String                 | 4-65   |

| Editing Waveforms            | 4-65   |

| Table Size                   | 4-67   |

| Waveform                     | 4-67   |

| Table Number                 | 4-67   |

| Waveform Definition          | 4-67   |

| Editing Sequence Parameters  | . 4-68 |

| LC0 – LC15                   | . 4-69 |

| Pipeline                     | . 4-69 |

| Vector Strobe                | 4-70   |

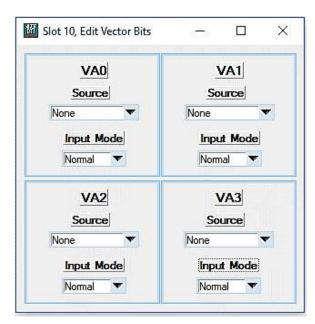

| Set Vector Bits              | 4-70   |

| Source                       | 4-71   |

| Input Mode                   | 4-71   |

| Set Vector Table             | 4-72   |

| Vector Bit Index             | 4-72   |

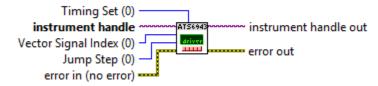

| Vector Jump Step             | 4-72   |

| Timing Set                   | 4-72   |

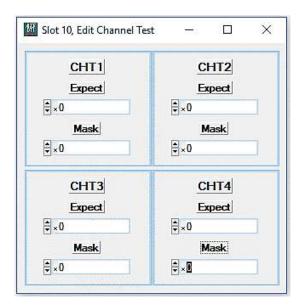

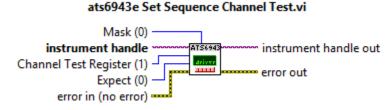

| Set Channel Test             | 4-73   |

| Expect                       | 4-73   |

| Mask                         | 4-73   |

| Editing Sequence Steps       | 4-74   |

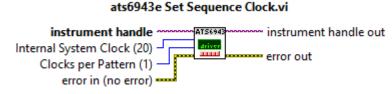

|      | Internal T0CLK                      | 4-75 |

|------|-------------------------------------|------|

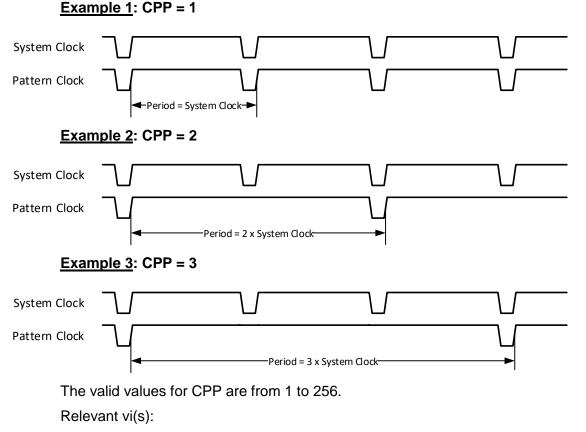

|      | Clocks per Pattern                  | 4-75 |

|      | CPP Phase and Window Triggering     | 4-76 |

|      | Timing Set                          | 4-76 |

|      | Last Step                           | 4-77 |

|      | Sequence Timeout                    | 4-77 |

|      | Gosub Return                        | 4-77 |

|      | Sequence Flag 1 and Sequence Flag 2 | 4-77 |

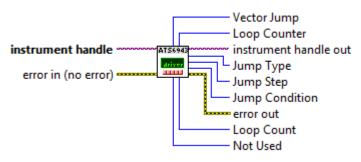

| ,    | Jump Type                           | 4-77 |

| ,    | Jump Step                           | 4-78 |

| ,    | Jump Condition                      | 4-78 |

|      | Loop Count                          | 4-79 |

|      | Loop Counter                        | 4-79 |

|      | Vector Jump                         | 4-80 |

|      | Pass Fail Clear                     | 4-80 |

|      | Step Record Mode                    | 4-80 |

|      | Timing                              | 4-81 |

|      | Patterns                            | 4-82 |

|      | Properties                          | 4-83 |

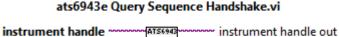

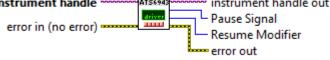

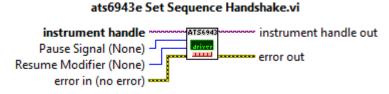

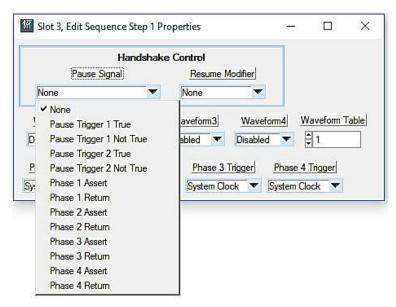

|      | Handshake Control                   | 4-83 |

|      | Pause Signal                        | 4-84 |

|      | Resume Modifier                     | 4-84 |

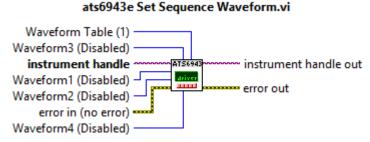

|      | Waveform Properties                 | 4-85 |

|      | Waveform1 – Waveform4               | 4-85 |

|      | Waveform Table                      | 4-85 |

|      | Phase Trigger Properties            | 4-85 |

| Exec | cute the Sequence                   | 4-85 |

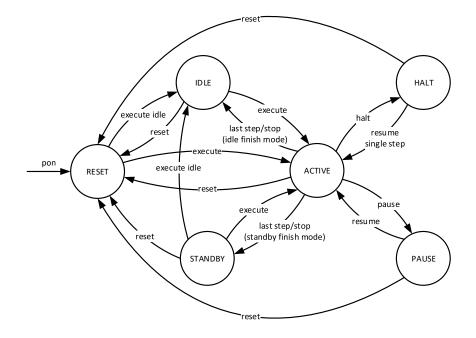

| Ex   | kecution Overview                   | 4-86 |

| Ex   | kecute Panel Indicators             | 4-88 |

|      | Idle LED                            | 4-88 |

|      | Active LED                          | 4-88 |

|      | Halt LED                            | 4-89 |

|      | Pause LED                           | 4-89 |

|      | Burst Error LED                     | 4-89 |

|      | Errors                              | 4-89 |

|      | D/R Alert                           | 4-89 |

|      | Sequence Active                     | 4-89 |

|      | Step Number                         | 4-89 |

|      | Pattern Address                     | 4-90 |

|      | Record Count                        | 4-90 |

|      | Timing Set                          | 4-90 |

| Execute Panel Modes and Settings 4-90 |

|---------------------------------------|

| Start/Arm Selector 4-90               |

| Channel Drivers                       |

| V+/ V                                 |

| Execute Idle Step 4-91                |

| Execute Step 4-91                     |

| Burst 4-91                            |

| Halt Mode 4-91                        |

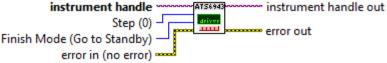

| Finish Mode 4-92                      |

| Finish Mode Step 4-93                 |

| Stop Mode                             |

| CRC Type                              |

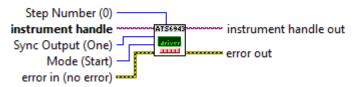

| Set Sync                              |

| Sync Number                           |

| Mode                                  |

| Step 4-94                             |

| Offset                                |

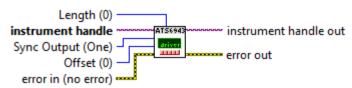

| Length 4-95                           |

| Execute Panel Command Buttons 4-95    |

| Execute Idle 4-95                     |

| Execute                               |

| Halt                                  |

| Resume                                |

| Stop 4-96                             |

| Reset 4-96                            |

| Master Reset 4-96                     |

| Deskew                                |

| Arm PG 4-97                           |

| Stop PG 4-97                          |

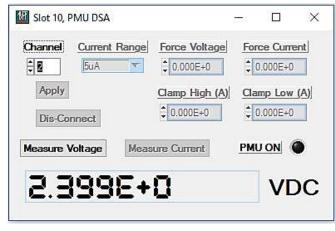

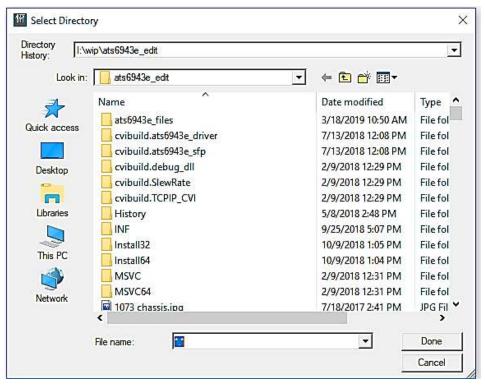

| PMU Operation                         |

| Channel                               |

| Current Range 4-98                    |

| Force Voltage                         |

| Force Current                         |

| Clamp High/Clamp Low                  |

| Current Clamps                        |

| Voltage Clamps                        |

| Apply                                 |

| Dis-connect                           |

| PMU ON                                |

| Measure Voltage                       |

| Measure Current                | 4-101 |

|--------------------------------|-------|

| Counter/Timer Operation        | 4-101 |

| Function                       | 4-101 |

| Input <1-3> Source             | 4-102 |

| Input <1-3> Slope              | 4-102 |

| Aperture                       | 4-102 |

| Trigger                        | 4-103 |

| Initiate                       | 4-103 |

| Results                        | 4-103 |

| Analyze the Execution Results  | 4-103 |

| Static Data                    | 4-104 |

| Response Delay                 | 4-105 |

| Stimulus                       | 4-105 |

| Response                       | 4-105 |

| Kept Data                      | 4-105 |

| Results                        | 4-106 |

| View                           | 4-107 |

| Save Results                   | 4-107 |

| CRC Save File Format           | 4-107 |

| Error Address Save File Format | 4-107 |

| Record Index Save File Format  | 4-108 |

| Record Data Save File Format   | 4-108 |

| CRCs Display                   | 4-108 |

| Error Address Display          | 4-109 |

| Record Index Display           | 4-110 |

| Record Data Display            | 4-111 |

| Status Indicator Panels        | 4-112 |

| Sequencer Events               | 4-112 |

| Enable                         | 4-114 |

| Condition                      | 4-114 |

| Event                          | 4-114 |

| Clear Event                    | 4-115 |

| Sequencer Data Panel           | 4-115 |

| Counter Active                 | 4-115 |

| Record Index Count             | 4-115 |

| Sync Error Step                | 4-115 |

| Sync Error Pattern Address     | 4-116 |

| Status                         | 4-116 |

| Driver/Receiver Events Panel   | 4-116 |

| Condition                      | 4-118 |

| PTE/NTE                        | 4-118 |

| Event                        | 4-118 |

|------------------------------|-------|

| Enable                       | 4-118 |

| Alert                        | 4-118 |

| Clear Event                  | 4-118 |

| Reset Alert                  | 4-118 |

| Driver/Receiver Data Panel   | 4-119 |

| PXI Trigger Readback Panel   | 4-120 |

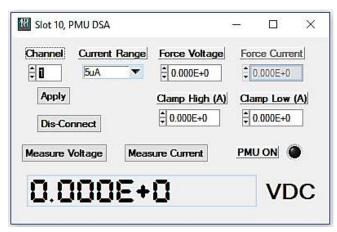

| Instrument Functions         | 4-120 |

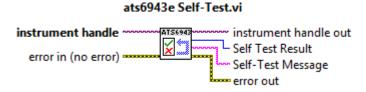

| Self Test                    | 4-120 |

| Full RAM Test                | 4-121 |

| Calibration Panel            | 4-122 |

| Calibrate Function           | 4-123 |

| Serial Number                | 4-124 |

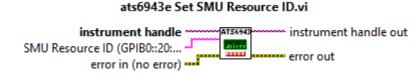

| SMU Resource Name            | 4-124 |

| Start Chan                   | 4-124 |

| Meas. Delay                  | 4-124 |

| End Channel                  | 4-125 |

| Run                          | 4-125 |

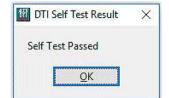

| Verify                       | 4-126 |

| Stop                         | 4-128 |

| Update                       | 4-128 |

| Update Firmware              | 4-128 |

| Voltage Monitor              | 4-129 |

| ADC Monitor                  | 4-129 |

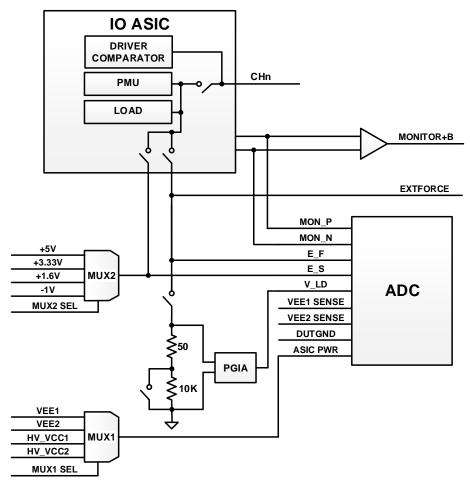

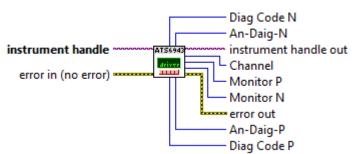

| ADC Signal                   | 4-131 |

| Channel                      | 4-131 |

| Mon-P Source                 | 4-131 |

| Mon-N Source                 | 4-131 |

| An-Diag-P Source             | 4-132 |

| An-Diag-N Source             | 4-132 |

| Diag Control Selections      | 4-132 |

| E_S/E_F Connect              | 4-132 |

| E_S Voltage                  | 4-132 |

| E_F Load                     | 4-132 |

| PGIA                         | 4-133 |

| Alert Temperature            | 4-134 |

| SFP Close Message            | 4-135 |

| LabVIEW vi's and API Library | 4-135 |

| Default Conditions           | 4-136 |

| LabVIEW Parameter Types      | 4-139 |

| C API Parameter Types        | 4-140 |

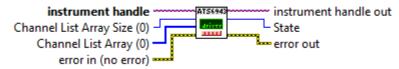

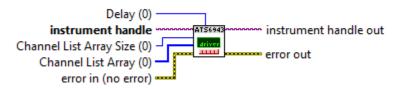

| LabVIEW vi Descriptions   | 4-141 |

|---------------------------|-------|

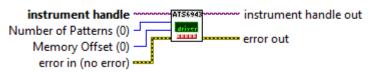

| Append Pattern            | 4-141 |

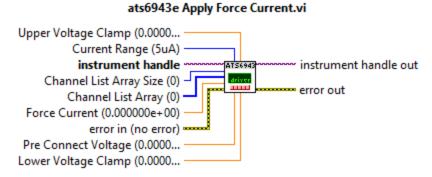

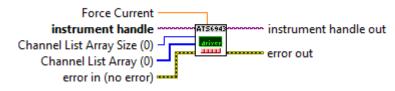

| Apply Force Current       | 4-142 |

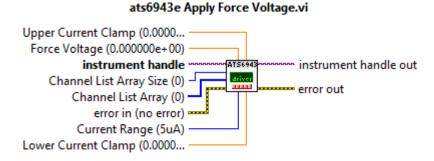

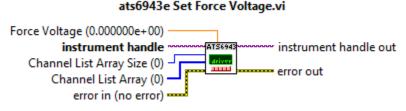

| Apply Force Voltage       | 4-143 |

| Arm Idle Sequence         | 4-144 |

| Arm Pulse Generator       | 4-144 |

| Arm Sequence              | 4-145 |

| Assign Pattern Set        | 4-145 |

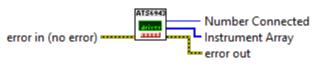

| Auto Connect To DTS       | 4-146 |

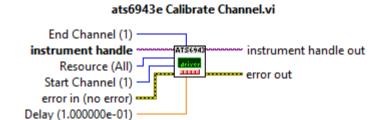

| Calibrate Channel         | 4-147 |

| Calibrate DTS Timing Bus  | 4-148 |

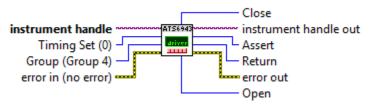

| Close                     | 4-149 |

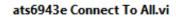

| Connect to All            | 4-149 |

| Connect To First          | 4-150 |

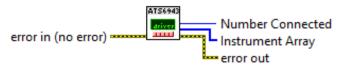

| Connect To Slot           | 4-151 |

| Counter Initiate Trigger  | 4-151 |

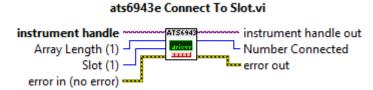

| Deskew DTI Channels       | 4-152 |

| Deskew DTS Channels       | 4-152 |

| Disconnect PMU            | 4-153 |

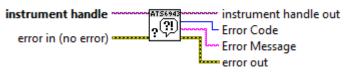

| Error Message             | 4-153 |

| Error-Query               | 4-157 |

| Execute Idle Sequence     | 4-158 |

| Execute Sequence          | 4-158 |

| Execute Static Pattern    | 4-159 |

| Flush Cache Data          | 4-160 |

| Halt Sequence             | 4-160 |

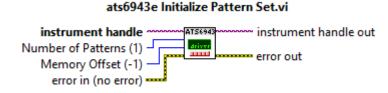

| Initialize Pattern Set    | 4-161 |

| Initialize Sequence Steps | 4-162 |

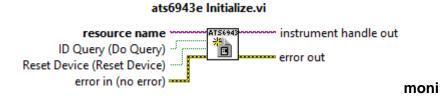

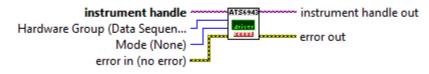

| Initialize                | 4-163 |

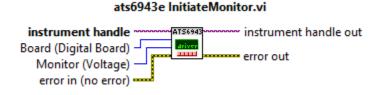

| Initiate Monitor          | 4-164 |

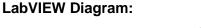

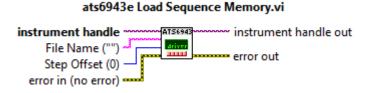

| Load Configuration        | 4-165 |

| Load DTI File             | 4-165 |

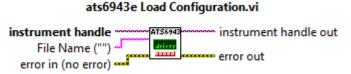

| Load Pattern Memory       | 4-166 |

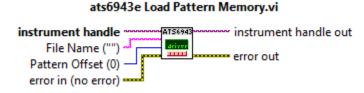

| Load Sequence Memory      | 4-167 |

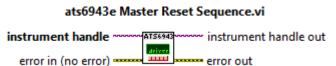

| Master Reset Sequence     | 4-167 |

| Measure Counter Result    | 4-168 |

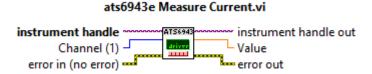

| Measure Current           | 4-169 |

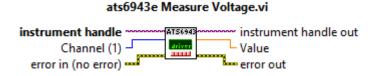

| Measure Voltage           | 4-169 |

| Query ADC Average         | 4-170 |

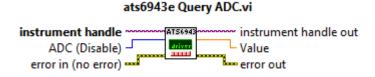

| Query ADC                 | 4-171 |

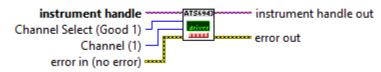

| Query Aux Channel Select  | 4-172 |

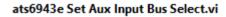

| Query Aux Input Bus Select 4-173      | 3 |

|---------------------------------------|---|

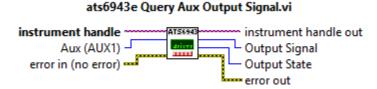

| Query Aux Output Signal 4-174         | ŀ |

| Query Burst Count 4-174               | ŀ |

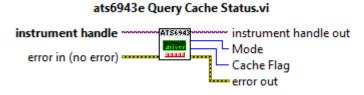

| Query Cache Status 4-175              | 5 |

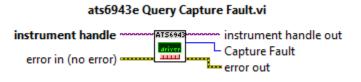

| Query Capture Fault 4-176             | ; |

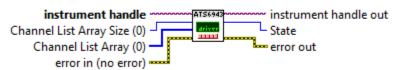

| Query Channel Connect 4-176           | 5 |

| Query Channel Function 4-177          | , |

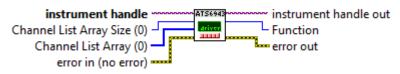

| Query Channel Load State 4-178        | 3 |

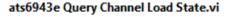

| Query Channel Mode 4-178              | 3 |

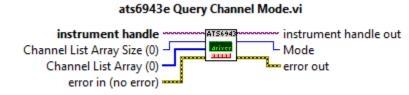

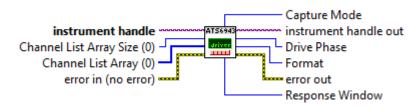

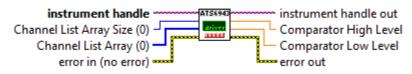

| Query Channel Parameters 4-179        | ) |

| Query Channel Sense Levels 4-180      | ) |

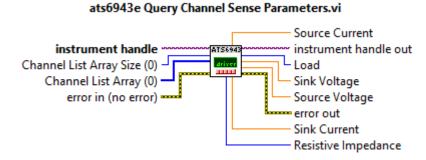

| Query Channel Sense Parameters 4-181  |   |

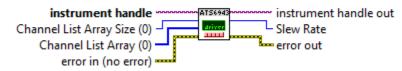

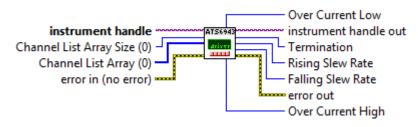

| Query Channel Slew Rate 4-182         | > |

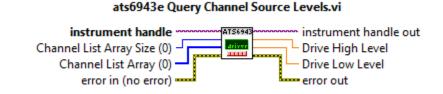

| Query Channel Source Levels 4-182     | > |

| Query Channel Source Parameters 4-183 | 3 |

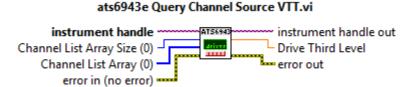

| Query Channel Source VTT 4-184        | ŀ |

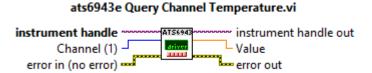

| Query Channel Temperature 4-185       | 5 |

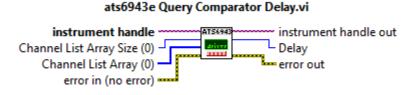

| Query Comparator Delay                | 5 |

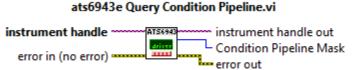

| Query Condition Pipeline 4-186        | 5 |

| Query Configuration                   | , |

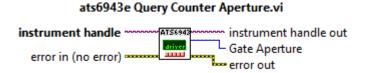

| Query Counter Aperture                | , |

| Query Counter Function                | 3 |

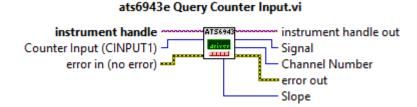

| Query Counter Input 4-189             | ) |

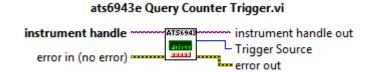

| Query Counter Trigger 4-189           | ) |

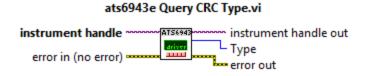

| Query CRC Type                        | ) |

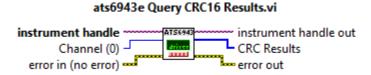

| Query CRC16 Results 4-190             | ) |

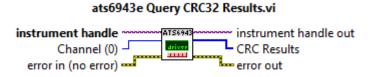

| Query CRC32 Results 4-191             |   |

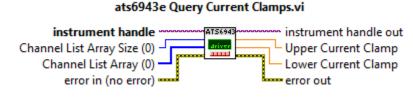

| Query Current Clamps                  | > |

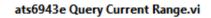

| Query Current Range 4-192             | > |

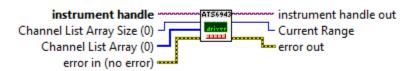

| Query Digital Board 4-193             |   |

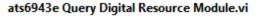

| Query Digital Resource Module 4-194   |   |

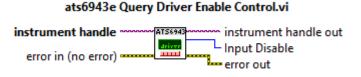

| Query Driver Enable Control           |   |

| Query Driver Fault State              | 5 |

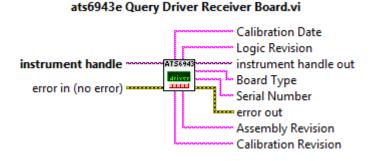

| Query Driver Receiver Board           | 5 |

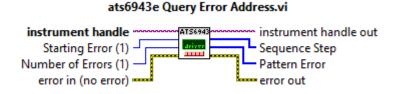

| Query Error Address 4-197             | , |

| Query Error Flags 4-197               | 7 |

| Query Error Parameters                | 3 |

| Query Event Enable                    |   |

| Query Execute Sequence                | ) |

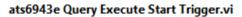

| Query Execute Start Trigger           |   |

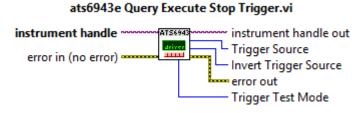

| Query Execute Stop Trigger 4-201      |   |

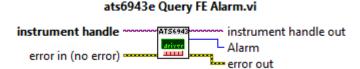

| Query FE Alarm                 | 4-201 |

|--------------------------------|-------|

| Query FE Alert                 | 4-202 |

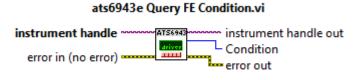

| Query FE Condition             | 4-203 |

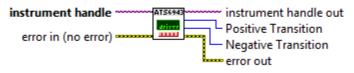

| Query FE Event Transition      | 4-204 |

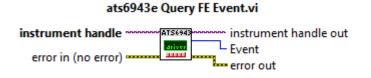

| Query FE Event                 | 4-205 |

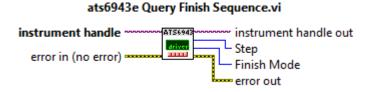

| Query Finish Sequence          | 4-205 |

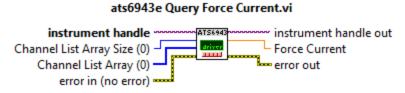

| Query Force Current            | 4-206 |

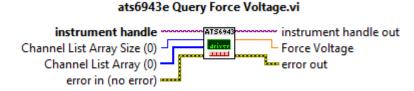

| Query Force Voltage            | 4-207 |

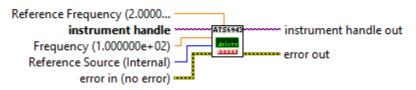

| Query Frequency Synthesizer    | 4-207 |

| Query Halt Mode                | 4-208 |

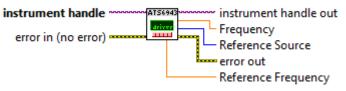

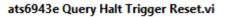

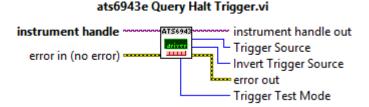

| Query Halt Trigger Reset       | 4-209 |

| Query Halt Trigger             | 4-209 |

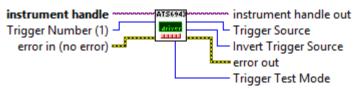

| Query Handshake Pause Trigger  | 4-210 |

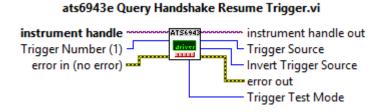

| Query Handshake Resume Trigger | 4-211 |

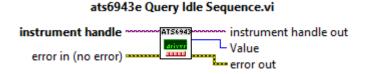

| Query Idle Sequence            | 4-213 |

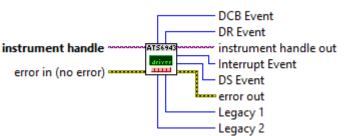

| Query Interrupt Condition      | 4-213 |

| Query Interrupt Event          | 4-214 |

| Query Interrupt Mode           | 4-215 |

| Query IO Max                   | 4-215 |

| Query Jump Trigger Reset       | 4-216 |

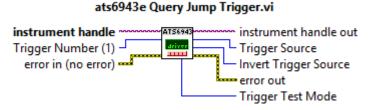

| Query Jump Trigger             | 4-217 |

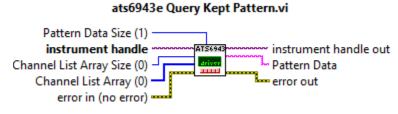

| Query Kept Pattern             | 4-218 |

| Query Master Clock Source      | 4-219 |

| Query Module Data              | 4-219 |

| Query Module Firmware          | 4-220 |

| Query Module FPGA              | 4-221 |

| Query Module Interconnect      | 4-222 |

| Query Monitor Signal           | 4-222 |

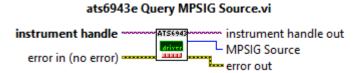

| Query MPSIG Source             | 4-223 |

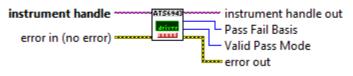

| Query Pass Fail Parameters     | 4-224 |

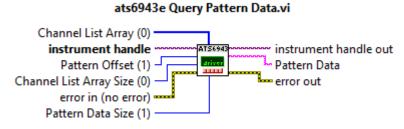

| Query Pattern Data             | 4-225 |

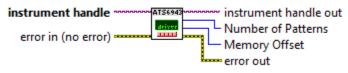

| Query Pattern Delay Timer      | 4-226 |

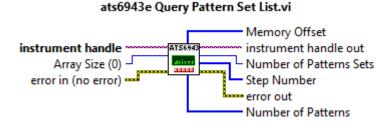

| Query Pattern Set List         | 4-227 |

| Query Pattern Set              | 4-228 |

| Query Pattern Test Enable      | 4-228 |

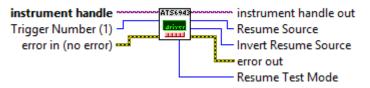

| Query Pattern Timer            | 4-229 |

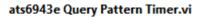

| Query Pause Trigger Reset      | 4-230 |

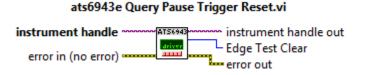

| Query Phase Resume Trigger     | 4-230 |

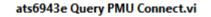

| Query PMU Connect              | 4-231 |

| Query Post Code                | 4-232 |

| Query Power Connect            | 4-234 |

| Query Power Settings 4-234           |

|--------------------------------------|

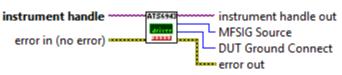

| Query Pulse Delay 4-235              |

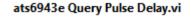

| Query Pulse Parameters 4-236         |

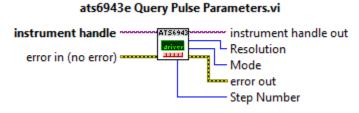

| Query Pulse Period 4-236             |

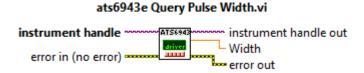

| Query Pulse Width 4-237              |

| Query Ram Test Results 4-237         |

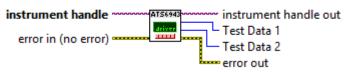

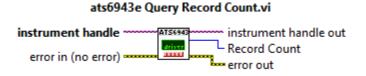

| Query Record Count 4-238             |

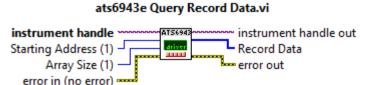

| Query Record Data 4-239              |

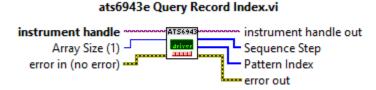

| Query Record Index 4-240             |

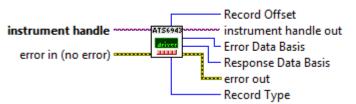

| Query Record Parameters 4-240        |

| Query Reference Load 4-241           |

| Query Reference Voltage 4-242        |

| Query Sequence Active 4-242          |

| Query Sequence Channel Test 4-243    |

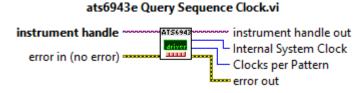

| Query Sequence Clock                 |

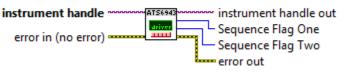

| Query Sequence Flags 4-244           |

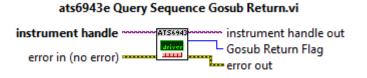

| Query Sequence Gosub Return          |

| Query Sequence Handshake             |

| Query Sequence Jump 4-246            |

| Query Sequence Last Step 4-247       |

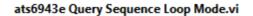

| Query Sequence Loop Mode 4-248       |

| Query Sequence Pass Fail Clear 4-248 |

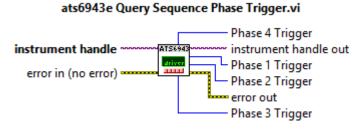

| Query Sequence Phase Trigger         |

| Query Sequence Record Mode 4-250     |

| Query Sequence Timeout Continue      |

| Query Sequence Timer                 |

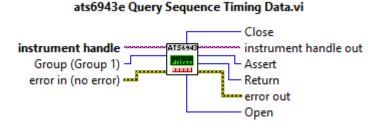

| Query Sequence Timing Data           |

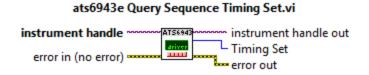

| Query Sequence Timing Set 4-252      |

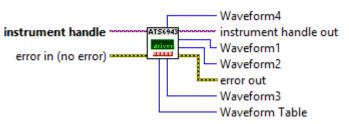

| Query Sequence Waveform              |

| Query Sequencer Attribute            |

| Query Sequencer Aux 4-255            |

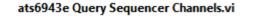

| Query Sequencer Channels             |

| Query Sequencer Condition            |

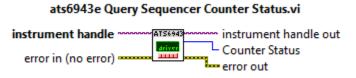

| Query Sequencer Counter Status 4-258 |

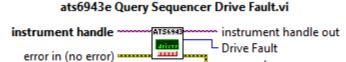

| Query Sequencer Drive Fault 4-258    |

| Query Sequencer Event                |

| Query Sequencer Record Index 4-259   |

| Query Sequencer Record Mode 4-260    |

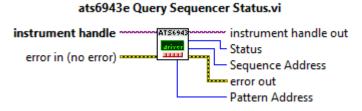

| Query Sequencer Status               |

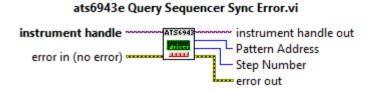

| Query Sequencer Sync Error           |

| Query Sequencer Timing Set           |

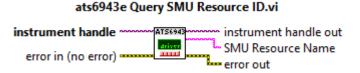

| Query SMU Resource ID4-26          | 3 |

|------------------------------------|---|

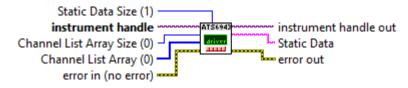

| Query Static Data                  | 3 |

| Query Static Mode4-264             | 4 |

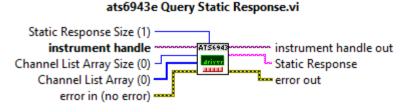

| Query Static Response4-26          | 5 |

| Query Static State                 | 6 |

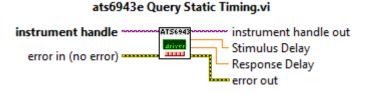

| Query Static Timing4-26            | 7 |

| Query Stop Mode                    | 7 |

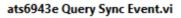

| Query Sync Event4-268              | 8 |

| Query Sync Parameters4-26          | 8 |

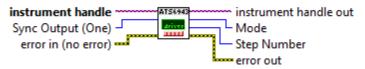

| Query System Clock Parameters4-269 | 9 |

| Query System Clock Source4-270     | 0 |

| Query Temperature Alarm            | 0 |

| Query Temperature Monitor          | 1 |

| Query Timing Mode                  | 1 |

| Query Timing Set Data4-272         | 2 |

| Query Trigger Levels               | 3 |

| Query TTL Triggers                 | 3 |

| Query Vector Jump Signal4-274      | 4 |

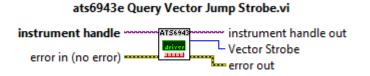

| Query Vector Jump Strobe4-275      | 5 |

| Query Vector Jump Table4-27        | 5 |

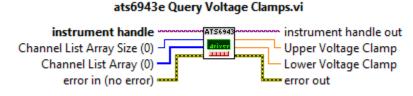

| Query Voltage Clamps4-270          | 6 |

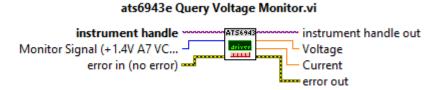

| Query Voltage Monitor4-27          | 7 |

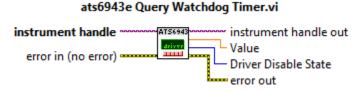

| Query Watchdog Timer4-278          | 8 |

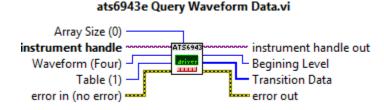

| Query Waveform Data4-278           | 8 |

| Query Waveform Table Size4-275     | 9 |

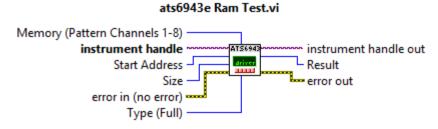

| Ram Test4-280                      | 0 |

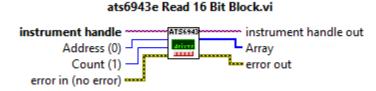

| Read 16 Bit Block4-282             | 2 |

| Read 16 Bit Register4-282          | 2 |

| Read 32 Bit Block4-28              | 3 |

| Read 32 Bit Register4-28           | 3 |

| Refresh Cache Data4-284            | 4 |

| Reset FE Alert4-284                | 4 |

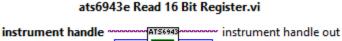

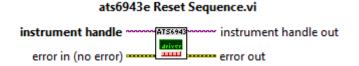

| Reset Sequence4-28                 | 5 |

| Reset4-28                          | 5 |

| Resume Sequence4-28                | 6 |

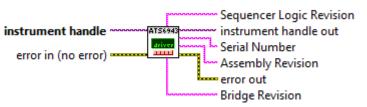

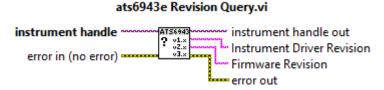

| Revision Query4-28                 | 7 |

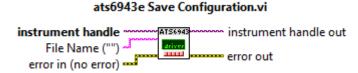

| Save Configuration                 | 7 |

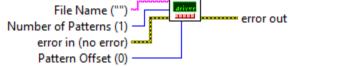

| Save Pattern Memory4-28            |   |

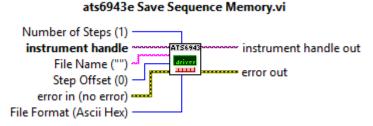

| Save Sequence Memory4-28           | 9 |

| Select Sequence Step               |   |

| Self-Test                          |   |

| Set Aux Channel Select 4-29        | 92 |

|------------------------------------|----|

| Set Aux Input Bus Select 4-29      | 93 |

| Set Aux Output Signal 4-29         | 94 |

| Set Burst Count 4-29               | 96 |

| Set Cache Mode 4-29                | 96 |

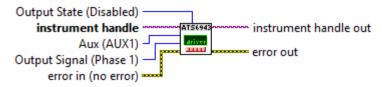

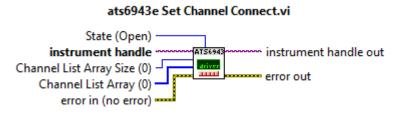

| Set Channel Connect 4-29           | 97 |

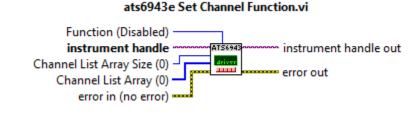

| Set Channel Function 4-29          | 98 |

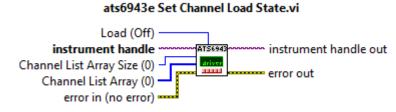

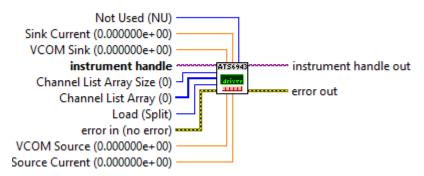

| Set Channel Load State 4-29        | 99 |

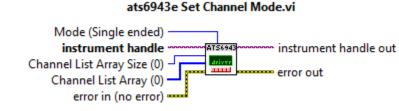

| Set Channel Mode 4-30              | 00 |

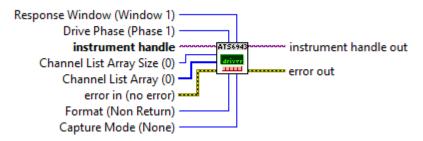

| Set Channel Parameters 4-30        | 01 |

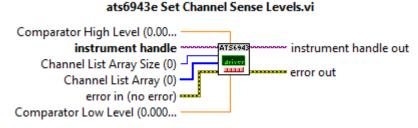

| Set Channel Sense Levels 4-30      | )4 |

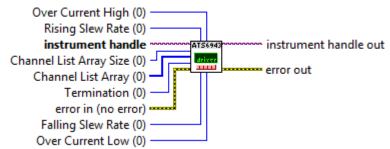

| Set Channel Sense Parameters 4-30  | )5 |

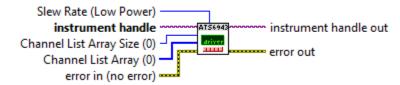

| Set Channel Slew Rate 4-30         | 26 |

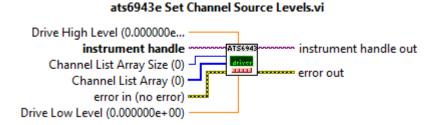

| Set Channel Source Levels 4-30     | )7 |

| Set Channel Source Parameters 4-30 | 30 |

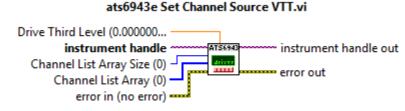

| Set Channel Source VTT 4-31        | 10 |

| Set Comparator Delay 4-31          | 10 |

| Set Condition Pipeline 4-31        |    |

| Set Counter Aperture 4-31          | 12 |

| Set Counter Function 4-31          | 12 |

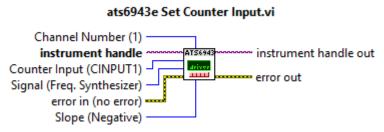

| Set Counter Input 4-31             | 13 |

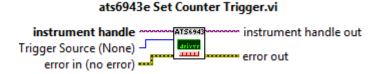

| Set Counter Trigger 4-31           | 15 |

| Set CRC Type 4-31                  | 15 |

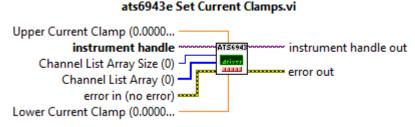

| Set Current Clamps 4-31            | 16 |

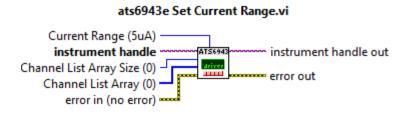

| Set Current Range 4-31             | 17 |

| Set Data Sequencer Memory 4-31     | 18 |

| Set Driver Enable Control 4-31     | 19 |

| Set Driver Enable 4-31             | 19 |

| Set Driver Fault State 4-32        | 20 |

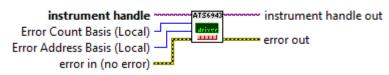

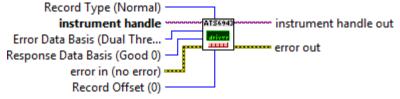

| Set Error Parameters 4-32          | 21 |

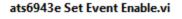

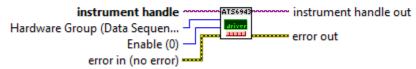

| Set Event Enable                   | 22 |

| Set Execute Start Trigger 4-32     | 24 |

| Set Execute Stop Trigger 4-32      | 25 |

| Set FE Event Transition 4-32       | 26 |

| Set Finish Sequence 4-32           | 27 |

| Set Force Connect                  | 28 |

| Set Force Current                  | 28 |

| Set Force Load 4-32                | 29 |

| Set Force Voltage 4-33             | 30 |

| Set Frequency Synthesizer 4-33     | 30 |

| Set Halt Mode                      | 32 |

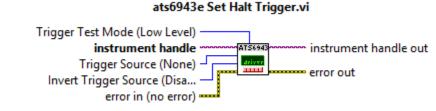

| Set Halt Trigger Reset       | 4-333 |

|------------------------------|-------|

| Set Halt Trigger             | 4-334 |

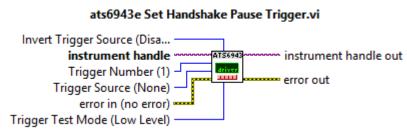

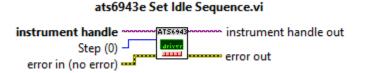

| Set Handshake Pause Trigger  | 4-335 |

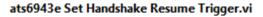

| Set Handshake Resume Trigger | 4-336 |

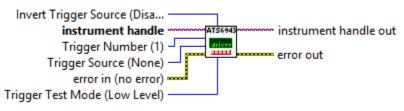

| Set Idle Sequence            | 4-338 |

| Set Interrupt Mode           | 4-338 |

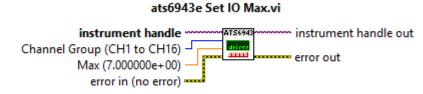

| Set IO Max                   | 4-339 |

| Set Jump Trigger Reset       | 4-340 |

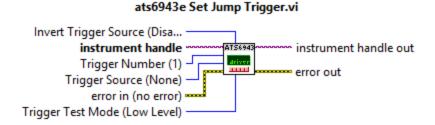

| Set Jump Trigger             | 4-340 |

| Set Master Clock Source      | 4-342 |

| Set Module Interconnect      | 4-343 |

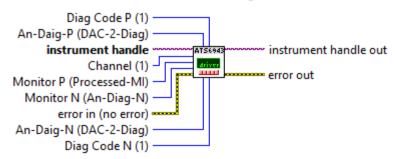

| Set Monitor Signal           | 4-344 |

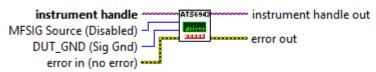

| Set MPSIG Source             | 4-345 |

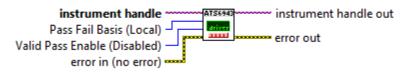

| Set Pass Fail Parameters     | 4-346 |

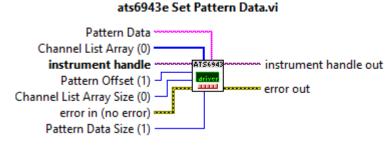

| Set Pattern Data             | 4-347 |

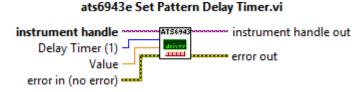

| Set Pattern Delay Timer      | 4-349 |

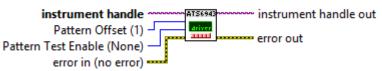

| Set Pattern Test Enable      | 4-349 |

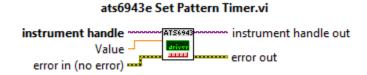

| Set Pattern Timer            | 4-350 |

| Set Pause Trigger Reset      | 4-351 |

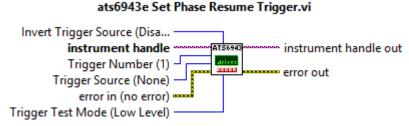

| Set Phase Resume Trigger     | 4-352 |

| Set Power Connect            | 4-353 |

| Set Power Settings           | 4-353 |

| Set Pulse Delay              | 4-354 |

| Set Pulse Parameters         | 4-355 |

| Set Pulse Period             | 4-356 |

| Set Pulse Width              | 4-356 |

| Set Record Parameters        | 4-357 |

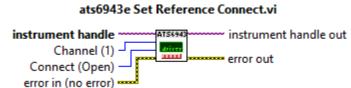

| Set Reference Connect        | 4-358 |

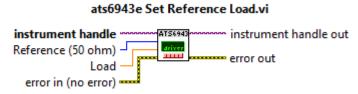

| Set Reference Load           | 4-359 |

| Set Reference Output         | 4-360 |

| Set Reference Voltage        | 4-360 |

| Set Sense Connect            | 4-361 |

| Set Sequence Channel Test    | 4-362 |

| Set Sequence Clock           | 4-363 |

| Set Sequence Flags           | 4-364 |

| Set Sequence Gosub Return    | 4-364 |

| Set Sequence Handshake       | 4-365 |

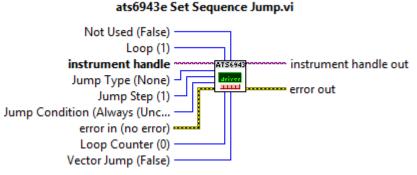

| Set Sequence Jump            | 4-366 |

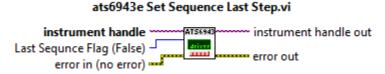

| Set Sequence Last Step       | 4-368 |

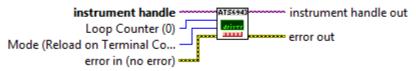

| Set Sequence Loop Mode       | 4-368 |

| Set Sequence Pass Fail Clear | 4-369 |

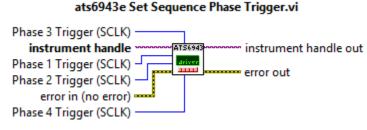

| Set Sequence Phase     | Trigger     | 4-370 |

|------------------------|-------------|-------|

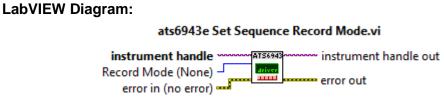

| Set Sequence Record    | d Mode      | 4-371 |

| Set Sequence Timeo     | ut Continue | 4-372 |

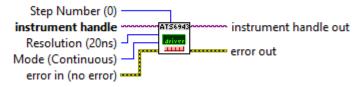

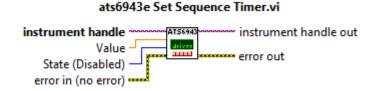

| Set Sequence Timer.    |             | 4-373 |

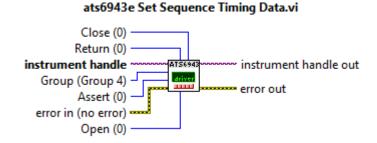

| Set Sequence Timing    | ) Data      | 4-373 |

| Set Sequence Timing    | 9 Set       | 4-375 |

| Set Sequence Wavef     | orm         | 4-376 |

| Set Sequencer Attrib   | ute         | 4-377 |

| Set Sequencer Recor    | rd Mode     | 4-378 |

| Set SMU Resource II    | D           | 4-378 |

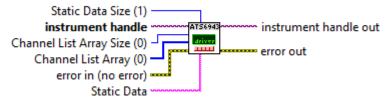

| Set Static Data        |             | 4-379 |

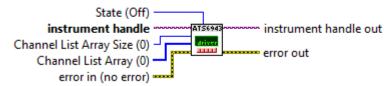

| Set Static Mode        |             | 4-380 |

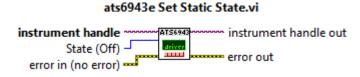

| Set Static State       |             | 4-381 |

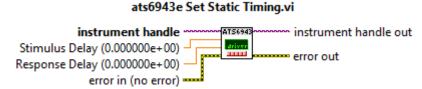

| Set Static Timing      |             | 4-381 |

| Set Stop Mode          |             | 4-382 |

| Set Sync Event         |             | 4-383 |

| Set Sync Parameters    |             | 4-384 |

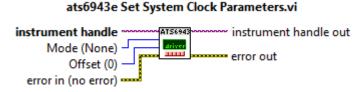

| Set System Clock Pa    | rameters    | 4-385 |

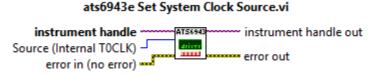

| Set System Clock So    | urce        | 4-386 |

| Set Temperature Alar   | ۳m          | 4-387 |

| Set Timing Mode        |             | 4-387 |

| Set Timing Set Data    |             | 4-388 |

| Set TTL Triggers       |             | 4-389 |

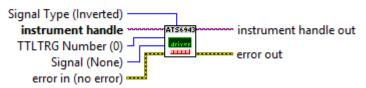

| Set Vector Jump Sigr   | nal         | 4-390 |

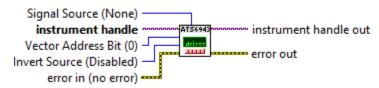

| Set Vector Jump Stro   | be          | 4-391 |

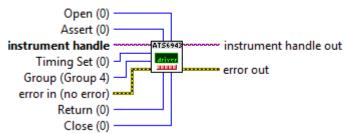

| Set Vector Jump Tab    | le          | 4-392 |

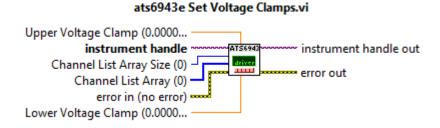

| Set Voltage Clamps     |             | 4-393 |

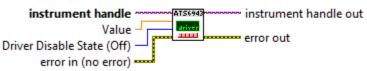

| Set Watchdog Timer.    |             | 4-394 |

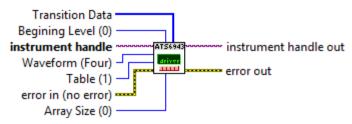

| Set Waveform Data      |             | 4-395 |

| Set Waveform Table     | Size        | 4-396 |

| Stop Pulse Generator   | r           | 4-397 |

| Stop Sequence          |             | 4-397 |

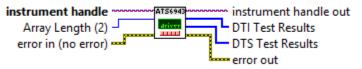

| Test DTS Timing Bus    | 5           | 4-398 |

| Update Cache Data      |             | 4-399 |

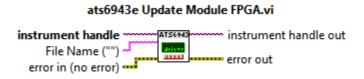

| Update Module FPG      | ۹           | 4-400 |

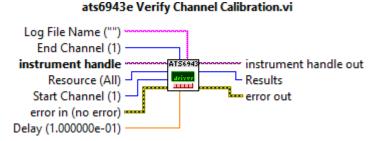

| Verify Channel Calibr  | ation       | 4-401 |

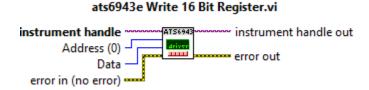

| Write 16 Bit Register. |             | 4-402 |

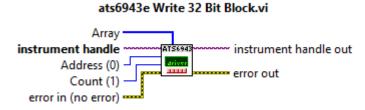

| Write 32 Bit Block     |             | 4-402 |

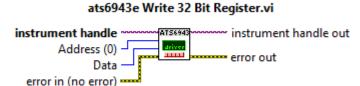

| Write 32 Bit Register. |             | 4-403 |

| Chapter 5              |             | 5-1   |

| Channel Calibration    |             | 5-1   |

| Performance Verification5-1   |

|-------------------------------|

| Environmental Conditions5-1   |

| Warm-up Period5-2             |

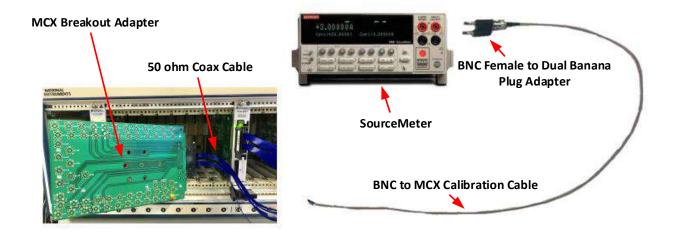

| Required Test Equipment5-2    |

| Calibration Interval5-2       |

| Calibration Temperature5-2    |

| Basic Setup5-3                |

| Calibration Procedures5-3     |

| Run Calibration Prompts5-4    |

| ADC Reference5-6              |

| Load Reference5-7             |

| ADC Gain5-8                   |

| Load PGIA5-10                 |

| Measure Voltage5-11           |

| DAC Overlap5-12               |

| PMU5-13                       |

| Drive Levels5-15              |

| Compare Levels5-17            |

| Active Load5-18               |

| Delete5-19                    |

| Chapter 66-1                  |

| Advanced Topics6-1            |

| DTS Signaling6-1              |

| Recording Sequence Results6-3 |

| Record Data6-3                |

| Record Memory6-3              |

| Record Index Memory6-3        |

| Error Address Memory6-3       |

| Error Counter6-4              |

| CRC Memory6-4                 |

| User Settings6-4              |

| Step Record Mode6-4           |

| Sequencer Record Mode6-5      |

| Record Type6-6                |

| Error Record Basis6-7         |

| Raw Record Basis6-8           |

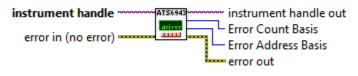

| Error Count Basis6-9          |

| Error Address Basis6-10       |

| CRC Type6-11                  |

| CRC Preload6-11               |

| CRC Algorithm6-12             |

| BERREN Bit                          | 6-13 |

|-------------------------------------|------|

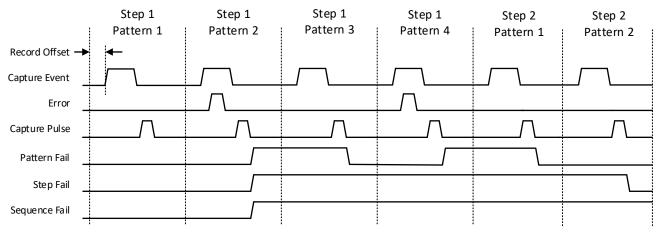

| Pass/Fail Flag Operation            | 6-14 |

| Pass/Fail Basics                    | 6-14 |

| Pass Fail Basis                     | 6-14 |

| Pass Fail Clear                     | 6-16 |

| Pass Valid Mode                     | 6-16 |

| Pipelining                          | 6-17 |

| Zero Pipeline Operation             | 6-18 |

| Non Zero Pipeline Operation         | 6-19 |

| Pipeline Preconditioning            | 6-22 |

| Jump on NOT Fail (PASS)             | 6-22 |

| Jump on NOT Pass (FAIL)             | 6-22 |

| Jumping                             | 6-23 |

| Pause and Halt                      | 6-26 |

| Pause Operation                     | 6-26 |

| Pause Examples                      | 6-28 |

| Pause Notes                         | 6-28 |

| Halt Operation                      | 6-29 |

| Internal Halt                       | 6-29 |

| External Halt                       | 6-32 |

| Halt Examples                       | 6-32 |

| Halt Notes                          | 6-33 |

| Sequencer Operation                 | 6-33 |

| Basic Sequence Step Flow            | 6-34 |

| Sequence Flow Example 1             | 6-35 |

| Sequence Flow Example 2             | 6-35 |

| Sequence Flow Example 3             | 6-35 |

| Sequence Flow Example 4             | 6-36 |

| Sequence Flow Example 5             | 6-36 |

| Pattern Control Instructions        | 6-36 |

| Pattern Control Looping             | 6-37 |

| Burst Counter                       | 6-37 |

| Burst Loop Example                  | 6-37 |

| Step Loop Counter                   | 6-37 |

| Step Loop Example 1                 | 6-38 |

| Step Loop Example 2                 | 6-38 |

| Pattern Control Jumping             | 6-39 |

| Pattern Control Instruction Details |      |

| PXI Backplane Trigger Bus           |      |

| Trigger Bus description             |      |

| Trigger Bus Applications            |      |

|                                     |      |

| Normal Operation6-4                             | 12 |

|-------------------------------------------------|----|

| Normal Operation Example6-4                     | 13 |

| Advanced Operation Examples6-4                  | 13 |

| Notes6-4                                        | 14 |

| SpecificationsA-                                | -1 |

| Data SequencerA-                                | -1 |

| Master ClockA-                                  | -1 |

| Timing CharacteristicsA-                        | -1 |

| Stimulus/CaptureA·                              | -2 |

| Recoding ModeA                                  | -3 |

| SequencerA·                                     | -3 |

| Counter/TimerA-                                 | -5 |

| Pulse GeneratorA                                | -6 |

| I/O ChannelsA-                                  | -6 |

| Power SupplyA-                                  | -8 |

| Peak and Dynamic Module Current ContributionsA- | -8 |

| Power AbsorbedA-                                | -8 |

| Environmental ConditionsA-                      | -8 |

| Glossary of Terms and Acronyms                  | .1 |

## **List of Figures**

| Figure 1-1 PXIe-6943 DTI 1-                          | -1 |

|------------------------------------------------------|----|

| Figure 1-2 Front Panel Connectors and Indicators 1-  | -4 |

| Figure 2-1 Module Installation Step 1 2-             | -1 |

| Figure 2-2 Module Installation Step 2 2-             | -2 |

| Figure 2-3 Module Installation Step 3 2-             |    |

| Figure 2-4 Module Installation Step 4 2-             | -2 |

| Figure 2-5 ETB Link Installation Levels              | -3 |

| Figure 2-6 J1 Cable Connectors                       | -4 |

| Figure 2-7 SFP POST Error Panel 2-                   | -4 |

| Figure 3-1 DTI Module Block Diagram                  | -1 |

| Figure 3-2 J1 Pin Numbering                          | -2 |

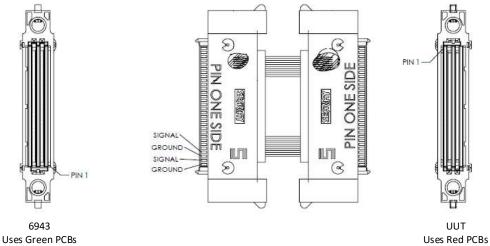

| Figure 3-3 Mating Cable                              | -4 |

| Figure 3-4 J1 Cable Pin 1 3-                         | -4 |

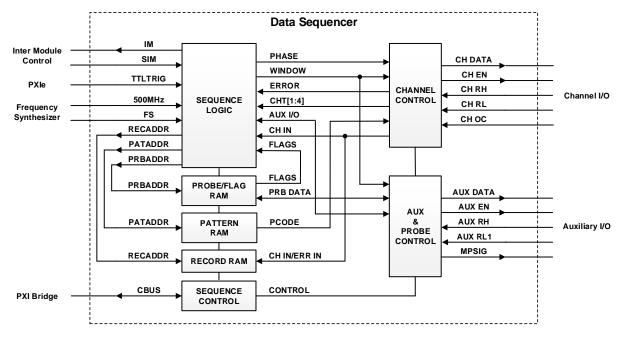

| Figure 3-5 Data Sequencer Block Diagram 3-           | -7 |

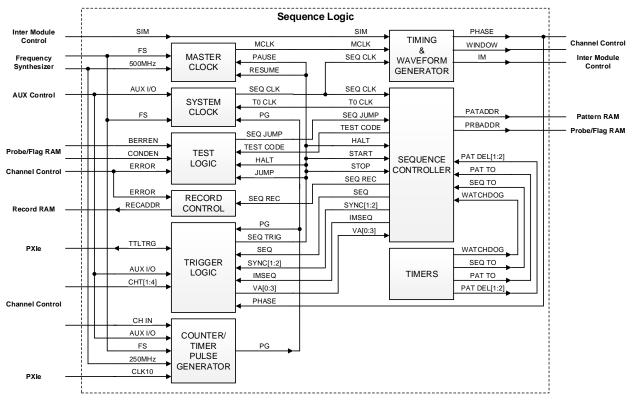

| Figure 3-6 Sequence Logic Block Diagram 3-           | -8 |

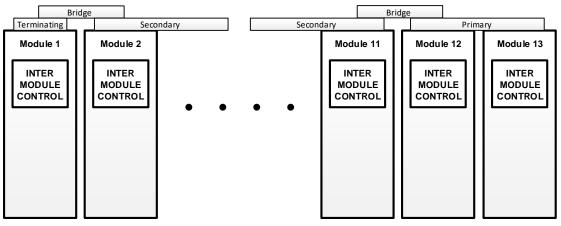

| Figure 3-7 ETB Links Multi Module System 3-1         | 11 |

| Figure 3-8 Inter Module Control Logic 3-1            | 11 |

| Figure 4-1 Test System Panel 4-                      | -2 |

| Figure 4-2 System Panel Menu Bar 4-                  | -2 |

| Figure 4-3 System Panel File Menu 4-                 | -2 |

| Figure 4-4 System Panel Close Prompt 4-              | -3 |

| Figure 4-5 System Panel Reset Prompt 4-              | -3 |

| Figure 4-6 System Panel System Menu 4-               | -3 |

| Figure 4-7 Configure DTS Error and Passed Pop Ups 4- | -4 |

| Figure 4-8 System Panel Help Menu 4-                 | -6 |

| Figure 4-9 Soft Front Panel About Panel 4-           | -6 |

| Figure 4-10 Company Information Panel 4-             | -7 |

| Figure 4-11 DTI Main Panel 4-                        | -8 |

| Figure 4-12 DTI Main Panel Menu Bar 4-               | -8 |

| Figure 4-13 DTI Panel File Menu 4-                   | -9 |

| Figure 4-14 Set DTI Data Panel 4-1                   | 10 |

| Figure 4-15 DTI Panel Config Menu 4-1                | 10 |

| Figure 4-16 DTI Panel Edit Menu 4-1                  | 11 |

| Figure 4-17 DTI Panel Execute Menu 4-1               | 12 |

| Figure 4-18 DTI Panel Instrument Menu 4-1            | 12 |

| Figure 4-19 Configure Module Panel 4-1               | 14 |

| Figure 4-20 Set PXI Triggers Panel                   | 16 |

| Figure 4-21 Configure D/R Properties Panel 4-1       | 18 |

| Figure 4-22 Configure Data Sequencer                      | 4-20 |

|-----------------------------------------------------------|------|

| Figure 4-23 Configure Clocks                              | 4-20 |

| Figure 4-24 Configure Timers                              | 4-23 |

| Figure 4-25 Configure Triggers Panel                      | 4-26 |

| Figure 4-26 Configure Pulse Generator                     | 4-29 |

| Figure 4-27 Data Sequencer Configure Settings Panel       | 4-31 |

| Figure 4-28 Attribute Panel                               |      |

| Figure 4-29 Configure Channels Panel                      | 4-39 |

| Figure 4-30 Configure Channel Properties Panel            | 4-43 |

| Figure 4-31 Configure Channel Properties Update           | 4-44 |

| Figure 4-32 Channel Properties Programmable Load Settings | 4-46 |

| Figure 4-33 Current Load                                  | 4-46 |

| Figure 4-34 Channel Mode Logic                            | 4-48 |

| Figure 4-35 Configure AUX Channels Panel                  | 4-49 |

| Figure 4-36 AUX Controls                                  | 4-50 |

| Figure 4-37 Editing the Data Sequencer                    | 4-53 |

| Figure 4-38 Phase Timing                                  | 4-54 |

| Figure 4-39 Edit Data Sequencer Timing Sets Panel         | 4-55 |

| Figure 4-40 Edit Sequence Step Timing Set Panel           | 4-55 |

| Figure 4-41 Disable Phase/Window                          | 4-56 |

| Figure 4-42 Edit Patterns Panel                           | 4-58 |

| Figure 4-43 Append Data Sequencer Pattern Sets Panel      | 4-58 |

| Figure 4-44 Assign Data Sequencer Pattern Sets Panel      | 4-59 |

| Figure 4-45 Pattern Set Sequencer Data Panel              | 4-60 |

| Figure 4-46 Pattern Set Data – View Menu                  | 4-60 |

| Figure 4-47 Goto Pattern Panel                            | 4-60 |

| Figure 4-48 Pattern Codes                                 | 4-61 |

| Figure 4-49 Pattern Set Data – File Menu                  | 4-62 |

| Figure 4-50 Edit Waveforms Panel Waveform 1               | 4-66 |

| Figure 4-51 Edit Waveforms Panel Waveform 5               | 4-67 |

| Figure 4-52 Data Sequencer Parameters Panel               | 4-69 |

| Figure 4-53 Edit Vector Bits Panel                        | 4-71 |

| Figure 4-54 Edit Vector Table Panel                       |      |

| Figure 4-55 Sequencer Channel Test Panel                  | 4-73 |

| Figure 4-56 Edit Sequence Step Panel                      | 4-74 |

| Figure 4-57 Sequence Step Data Panel                      | 4-75 |

| Figure 4-58 Edit Timing Set Panel                         | 4-81 |

| Figure 4-59 Initialize Step Pattern Set Panel             | 4-82 |

| Figure 4-60 Edit Pattern Set Panel                        |      |

| Figure 4-61 Sequence Step Properties Panel                | 4-83 |

| Figure 4-62 Executing a Sequence Panel                    | 4-86 |

| Figure 4-63 Execute State Diagram                       |        |

|---------------------------------------------------------|--------|

| Figure 4-64 Set Sync Panel                              |        |

| Figure 4-65 PMU Panel Dynamic Channel                   | . 4-97 |

| Figure 4-66 PMU Panel PMU FV Channel                    | . 4-98 |

| Figure 4-67 PMU Panel PMU FI Channel                    | . 4-98 |

| Figure 4-68 Timer/Counter Panel                         | 4-101  |

| Figure 4-69 Execute View Menu                           | 4-104  |

| Figure 4-70 Static Data Panel                           | 4-104  |

| Figure 4-71 Kept Data Panel                             | 4-106  |

| Figure 4-72 View Results Data Panel                     |        |

| Figure 4-73 View CRC Panel                              | 4-109  |

| Figure 4-74 View Errors Address Panel                   |        |

| Figure 4-75 Execution Results View Menu                 | 4-110  |

| Figure 4-76 View Errors Address Panel Hex               |        |

| Figure 4-77 Record Index Panel                          |        |

| Figure 4-78 View Record Data Panel                      |        |

| Figure 4-79 Sequencer Event Status Panel                |        |

| Figure 4-80 Sequencer Data Panel                        |        |

| Figure 4-81 Driver/Receiver Events Panel                |        |

| Figure 4-82 Driver/Receiver Data Panel                  |        |

| Figure 4-83 PXI Trigger Readback Panel                  | 4-120  |

|                                                         |        |

| Figure 4-85 Full RAM Test Results Panel                 | 4-122  |

| Figure 4-84 Self Test Result Message                    |        |

|                                                         |        |

| Figure 4-88 Confirm Calibrate Panel                     | 4-125  |

| Figure 4-89 Calibrate Warm-up Panel                     | 4-125  |

| Figure 4-90 Connect EXTFORCE to SMU                     | 4-125  |

| Figure 4-91 Calibrate Run Panel                         | 4-126  |

| Figure 4-92 Confirm Verify Panel                        | 4-126  |

| Figure 4-93 Verify Select Directory Panel               | 4-127  |

| Figure 4-94 Verify Warm-up Panel                        | 4-127  |

| Figure 4-95 Verify Run Panel                            | 4-128  |

| Figure 4-96 Voltage Monitoring Panel                    | 4-129  |

| Figure 4-97 ADC Monitor Panel                           | 4-130  |

| Figure 4-98 ADC Monitor Logic                           | 4-130  |

| Figure 4-99 Chip Temperature                            | 4-134  |

| Figure 4-100 SFP Close Message                          | 4-135  |

| Figure 4-101 SFP Reset Message                          | 4-135  |

| Figure 5-1 Setup                                        |        |

| Figure 5-2: Invoke the Calibrate DTI Panel from the SFP | 5-3    |

| Figure 5-3 Calibration Prompt                                         | 5-4  |

|-----------------------------------------------------------------------|------|

| Figure 5-4 Calibration Function List                                  | 5-4  |

| Figure 5-5 Calibration Run Confirmation                               | 5-5  |

| Figure 5-6 Calibration Warmup Prompt                                  | 5-5  |

| Figure 5-7 SMU Connect Prompt                                         | 5-5  |

| Figure 5-8 ADC Reference Calibration                                  | 5-6  |

| Figure 5-9 ADC Reference Complete                                     | 5-7  |

| Figure 5-10 Load Reference Calibration                                | 5-8  |

| Figure 5-11 Load Reference Complete                                   | 5-8  |

| Figure 5-12 ADC Gain Calibration                                      | 5-9  |

| Figure 5-13 ADC Gain Complete                                         | 5-9  |

| Figure 5-14 Load PGIA Calibration                                     | 5-10 |

| Figure 5-15 Load PGIA Complete                                        | 5-11 |

| Figure 5-16 Measure Voltage Calibration                               | 5-11 |

| Figure 5-17 Measure Voltage Complete                                  | 5-12 |

| Figure 5-18 DAC Overlap Calibration                                   | 5-13 |

| Figure 5-19 DAC Overlap Complete                                      | 5-13 |

| Figure 5-20 PMU Calibration                                           | 5-15 |

| Figure 5-21 PMU Complete                                              | 5-15 |

| Figure 5-22 Drive Level Calibration                                   | 5-16 |

| Figure 5-23 Drive Levels Complete                                     | 5-17 |

| Figure 5-24 Compare Level Calibration                                 | 5-17 |

| Figure 5-25 Compare Levels Complete                                   | 5-18 |

| Figure 5-26 Active Load Calibration                                   | 5-19 |

| Figure 5-27 Active Load Complete                                      | 5-19 |

| Figure 5-28 Delete Calibration Prompt                                 | 5-20 |

| Figure 6-1: Configure PXI Triggers                                    | 6-2  |

| Figure 6-2: Step Record Mode Control                                  | 6-5  |

| Figure 6-3 Sequencer Record Mode Control                              | 6-6  |

| Figure 6-4 Record Type Settings                                       | 6-7  |

| Figure 6-5 Error Record Basis Settings                                | 6-7  |

| Figure 6-6 Raw Record Basis Settings                                  | 6-9  |

| Figure 6-7 Error Count Basis Settings                                 | 6-9  |

| Figure 6-8 Error Address Basis Settings                               | 6-10 |

| Figure 6-9 CRC Type Settings                                          | 6-11 |

| Figure 6-10 CRC Preload Settings                                      | 6-12 |

| Figure 6-11 CRC Algorithm Settings                                    | 6-12 |

| Figure 6-12 Setting the BERREN Bit in the Edit Pattern Set Step Panel | 6-13 |

| Figure 6-13 Setting the Pass/Fail Basis                               | 6-15 |

| Figure 6-14 Setting the CONDEN Flag                                   | 6-15 |

| Figure 6-15 Setting Pass Fail Clear                                   | 6-16 |

| Figure 6-16 Setting Pass Valid Mode                | 6-17 |

|----------------------------------------------------|------|

| Figure 6-17 Setting the Pipeline Depth             | 6-17 |

| Figure 6-18 Zero Pipeline Timing Diagram           | 6-19 |

| Figure 6-19 Non Zero Pipeline Timing Diagram       | 6-21 |

| Figure 6-20 Setting the Jump Pass Fail Setting     | 6-21 |

| Figure 6-21 Setting the Sequence Step Jump Type    | 6-23 |

| Figure 6-22 Sequence Step Normal and Jump Settings | 6-24 |

| Figure 6-23 Setting the Jump Condition             | 6-25 |

| Figure 6-24 Selecting the Pause Signal             | 6-27 |

| Figure 6-25 Selecting the Resume Modifier          | 6-27 |

| Figure 6-26 Setting the Halt Mode                  | 6-30 |

| Figure 6-27 Setting the Sync Pulse                 | 6-31 |

## **List of Tables**

| Table 1-1 PXIe-2461 LED Indicators                        | 1-4  |

|-----------------------------------------------------------|------|

| Table 1-2 ETB Links, Cables and Adapter Accessories       | 1-6  |

| Table 1-3 ETB Kit Descriptions                            | 1-8  |

| Table 2-1 DB POST Error Description                       | 2-5  |

| Table 2-2 DR POST Error Description                       | 2-6  |

| Table 3-1 Front Panel J1 Connector Part Number            | 3-1  |

| Table 3-2 J1 Pinout                                       | 3-2  |

| Table 3-3 J1 Signal Description                           | 3-3  |

| Table 3-4 J1 Cable Pinout                                 | 3-5  |

| Table 3-5 AUX I/O Logic and Termination                   | 3-12 |

| Table 3-6 Analog Voltage Power On Voltages and Thresholds | 3-13 |

| Table 4-1 Configure DTS Error Bits                        | 4-4  |

| Table 4-2 Calibrate DTS Pop Up Panel Messages             | 4-5  |

| Table 4-3 Inter-Module Mode Settings                      | 4-15 |

| Table 4-4 Delay Signal Settings                           | 4-16 |

| Table 4-5 PXITRG Signal Settings                          | 4-17 |

| Table 4-6 MFSIG Settings                                  | 4-18 |

| Table 4-7 MPSIG Source                                    | 4-19 |

| Table 4-8 Sequencer Record Mode Settings                  | 4-19 |

| Table 4-9 Master Clock Source Settings                    | 4-20 |

| Table 4-10 System Clock Source Settings                   | 4-21 |

| Table 4-11 External Mode Settings                         | 4-21 |

| Table 4-12 Synthesizer Ref Source Settings                | 4-22 |

| Table 4-13 Watchdog Action                                | 4-24 |

| Table 4-14 Watchdog Timer Resolution Ranges               | 4-24 |

| Table 4-15 Sequence Timeout State Action                  | 4-25 |

| Table 4-16 Trigger Settings                               | 4-27 |

| Table 4-17 Trigger Source Settings                        | 4-27 |

| Table 4-18 Trigger Test Condition Settings                | 4-28 |

| Table 4-19 Trigger Input Mode Settings                    | 4-28 |

| Table 4-20 Trigger Event Clear Settings                   | 4-29 |

| Table 4-21 Pulse Generator Mode Settings                  | 4-30 |

| Table 4-22 Error Record Basis Settings                    | 4-31 |

| Table 4-23 Raw Record Basis Settings                      | 4-32 |

| Table 4-24 Record Type Settings                           | 4-33 |

| Table 4-25 Error Count Basis Settings                     | 4-33 |

| Table 4-26 Error Address Basis Settings                   | 4-33 |

| Table 4-27 Timing Mode Settings                           | 4-34 |

| Table 4-28 Output-to-Input Disable Settings     | . 4-34 |

|-------------------------------------------------|--------|

| Table 4-29 Pass Fail Basis Settings             | . 4-34 |

| Table 4-30 Pass Valid Mode Settings             | . 4-35 |

| Table 4-31 Drive Fault Settings                 | . 4-35 |

| Table 4-32 Jump Pass Fail Settings              | . 4-36 |

| Table 4-33 Phase 3 Mode Settings                | . 4-36 |

| Table 4-34 Window 3 Mode Settings               | . 4-37 |

| Table 4-35 CRC Preload Settings                 | . 4-37 |

| Table 4-36 CRC Algorithm and Mask Settings      | . 4-38 |

| Table 4-37 Static State Settings                | . 4-38 |

| Table 4-38 Channel Function Settings            | . 4-40 |

| Table 4-39 Stimulus Signal Settings             | . 4-40 |

| Table 4-40 Stimulus Format Settings             | . 4-41 |

| Table 4-41 Capture Signal Settings              | . 4-42 |

| Table 4-42 Capture Mode Settings                | . 4-42 |

| Table 4-43 Static Mode Settings                 | . 4-43 |

| Table 4-44 Slew Settings                        | . 4-45 |

| Table 4-45 Load State Settings                  | . 4-46 |

| Table 4-46 Active Load Settings                 | . 4-47 |

| Table 4-47 Channel Connect Settings             | . 4-48 |

| Table 4-48 Single Ended Comparator Logic States | . 4-49 |

| Table 4-49 Differential Comparator Logic States | . 4-49 |

| Table 4-50 AUX Output State Settings            | . 4-51 |

| Table 4-51 AUX Source Settings                  | . 4-52 |

| Table 4-52 Input Bus Select Source Settings     | . 4-52 |

| Table 4-53 Pattern Codes                        | . 4-62 |

| Table 4-54 ASCII Hex File Data Format           | . 4-63 |

| Table 4-55 ASCII Hex File Flag Format           | . 4-63 |

| Table 4-56 Binary Block Format                  | . 4-64 |

| Table 4-57 Binary File Data Format              | . 4-65 |

| Table 4-58 Binary File Flag Format              | . 4-65 |

| Table 4-59 Waveform Table Size Settings         | . 4-67 |

| Table 4-60: Vector Strobe Settings              | . 4-70 |

| Table 4-61 Vector Bit Source Settings           | . 4-71 |

| Table 4-62 Vector Bit Input Mode Settings       | . 4-71 |

| Table 4-63 Jump Condition Settings              | . 4-79 |

| Table 4-64 Step Record Mode Settings            | . 4-80 |

| Table 4-65 Step Record Mode Settings            | . 4-81 |

| Table 4-66 Handshake Pause Signal               | . 4-84 |

| Table 4-67 Handshake Modifier Settings          | . 4-85 |

| Table 4-68 Execute State Description            | . 4-87 |

| Table 4-69 Execute State Transition Description                            | 4-88  |

|----------------------------------------------------------------------------|-------|

| Table 4-70 Channel Drivers Settings                                        | 4-90  |

| Table 4-71 Halt Mode Settings                                              | 4-92  |

| Table 4-72 Finish Mode Settings                                            | 4-92  |

| Table 4-73 Stop Mode Settings                                              | 4-93  |

| Table 4-74 CRC Type Settings                                               | 4-93  |

| Table 4-75 Sync Mode Settings                                              | 4-94  |

| Table 4-76 Current Range Settings                                          | 4-98  |

| Table 4-77 Counter/Timer Function Settings                                 | 4-102 |

| Table 4-78 Counter/Timer Input <1-3> Source                                | 4-102 |

| Table 4-79 Counter/Timer Input <1-3> Slope                                 | 4-102 |

| Table 4-80 Counter/Timer Aperture                                          | 4-103 |

| Table 4-81 Timer/Counter Trigger Source                                    | 4-103 |

| Table 4-82 Static Stimulus Settings                                        | 4-105 |

| Table 4-83 Static Stimulus Settings                                        | 4-105 |

| Table 4-84 Results View Settings                                           | 4-107 |

| Table 4-85 Sequence Enable/Condition/Event Bit Descriptions                | 4-114 |

| Table 4-86 Sequence Status Bit Descriptions                                | 4-116 |

| Table 4-87 Sequence Status Bit Descriptions                                | 4-117 |

| Table 4-88 Self-Test Result Code Descriptions                              | 4-121 |

| Table 4-89 Calibrate Function Settings                                     | 4-124 |

| Table 4-90 Update Firmware File Prefix                                     | 4-128 |

| Table 4-91 ADC Signal Settings                                             | 4-131 |

| Table 4-92 LabVIEW vi and API Class Hierarchy                              | 4-136 |

| Table 4-93 Power on/Reset Defaults                                         | 4-139 |

| Table 4-94 Error Codes and Messages                                        | 4-157 |

| Table 5-1 Calibration Functions                                            | 5-1   |

| Table 5-2 Required Calibration Equipment                                   | 5-2   |

| Table 6-1 ETB Signal Description                                           | 6-2   |

| Table 6-2 Backplane DTS Signals                                            | 6-2   |

| Table 6-3 Step Record Mode Effect on Record Memory                         | 6-5   |

| Table 6-4 Error Record Basis Results                                       | 6-8   |

| Table 6-5 Error Counter Operation with Error Count Basis Settings          | 6-10  |

| Table 6-6 Error Address Memory Operation with Error Address Basis Settings | 6-10  |

| Table 6-7 CRC Type Polynomial Feedback                                     |       |

| Table 6-8 CRC Preload Settings                                             | 6-12  |

| Table 6-9 Sequence Step Flow Example Definitions                           |       |

| Table 6-10 Sequence Flow Example 1                                         | 6-35  |

| Table 6-11 Sequence Flow Example 2                                         | 6-35  |

| Table 6-12 Sequence Flow Example 3                                         |       |

| Table 6-13 Sequence Flow Example 4                                         | 6-36  |

| Table 6-14 Sequence Flow Example 5  | 6-36 |

|-------------------------------------|------|

| Table 6-15 Burst Loop Example       | 6-37 |

| Table 6-16 Step Loop Example 1      | 6-38 |

| Table 6-17 Step Loop Example 2      | 6-38 |

| Table 6-18 Pattern Control Acronyms | 6-39 |

| Table 6-19 Pattern Control Flow     | 6-41 |

### **Document Change History**

| Revision | Date       | Description of Change |

|----------|------------|-----------------------|

| А        | 03/08/2021 | Initial Release       |

|          |            |                       |

|          |            |                       |

This page was left intentionally blank.

# Chapter 1 Overview and Features

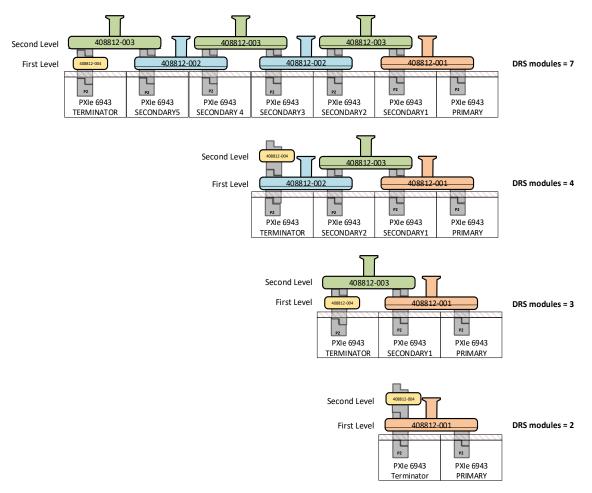

This manual provides information necessary to set up and operate the PXIe 6943 32-Channel module. A single PXIe 6943 is referred to as a Digital Test Instrument (**DTI**). Up to thirteen DTIs can be coupled and synchronized as a Digital Test Suite (**DTS**).

Throughout this manual, "DTI" is used to refer to the PXIe 6943 and "DTS" is used to refer to two or more PXIe 6943s coupled together.

## Introduction

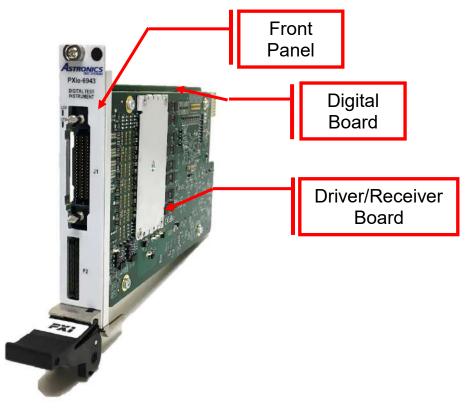

The PXIe-6943 DTI (see Figure 1-1) is a high performance, 32-channel, 50 MHz digital I/O system. The instrument is designed to be used in a PXIe compatible mainframe and conforms to PXI Express Hardware Specification Revision 1.1.

Figure 1-1 PXIe-6943 DTI

The DTI provides a high speed data sequencer and 32 high-performance digital I/O channels in a space-saving, single-wide PXIe module. The DTI operates at data rates up to 50 MHz with 1 ns edge placement and less than 3 ns channel-to-channel skew.

#### **Designed for High Reliability**

The comprehensive thermal design ensures reliability with excellent cooling, monitoring, and protection. Each high-power module is equipped with a customdesigned heat sink to provide optimal cooling. An on-board temperature monitor protects the pin electronics devices from overheating and provides overtemperature shutdown.

#### Advanced Features for Modern Digital Test Development

The DTI is designed for today's challenging digital test system applications through innovative design. The flexible Field Programmable Gate Array (FPGA) design enables the DTI to meet special user and legacy requirements. The high-speed Data Sequencer provides control over test patterns, timing, and format.

#### **Innovative Software Tools Speed Test Development**

The API driver and Digital Test Instrument Layer support third-party test development tools to ease development and integration into popular test environments

#### Scalable Design

Built-in scalability and modular design enable linking of up to 13 modules to create a Digital Test Suite (DTS). Individual modules in the DTS can operate as an independent digital instrument or be combined as a digital subsystem.

#### **High-Speed Data Sequencer**

The high-speed data sequencer provides state-of-the-art control over digital test patterns. Sequencer logic supports full unit under test (UUT) handshaking and controls timing, format, pattern data, looping, and conditional testing. The sequencer includes definable, standby, and idle sequences.

#### **Triggering and Synchronization**

The DTI features extensive control over digital testing to synchronize with other test instruments and control digital test sequencing. The DTI accepts triggers from the PXI TTL Trigger Bus, front panel Auxiliary inputs, or from any channel, and provides two sync outputs per DTI. Triggers can be used to synchronize the DTI with other instruments and as a test input for test sequence control. Sync outputs can be offset with reference to the start of a sequence or a sequence step.

#### Instrument Soft Front Panel

The soft front panel software provides interactive control of the DTI. The intuitive graphical interface enables setup and configuration, calibration, and sequencer control. Channels may be set up either individually or in groups.

#### Automatic Test Program Generation (ATPG)

The optional ATPG provides an interface to IEEE-Std-1445 formatted files that can be generated from automatic test program generators such as LASAR to seamlessly integrate with the DTI. This interface provides the capability for the system to utilize the various features of IEEE-Std-1445 to support guided probe, fault dictionary, and complex patterns and timing set(s).

#### **Migration Tools and Translators**

The optional Migration Tools and Translators support many legacy test systems from a variety of manufacturers. Test programs from supported systems are easily translated without extensive code rewriting.

### **I/O Features**

The DTI I/O features:

- Channels: 32 single-ended variable voltage.

- Dual threshold or differential comparator mode.

- Voltage range: -2 V to +7 V with an output swing of up to 9 V

- Relay Isolation on all 32 I/O channels.

- PMU Capabilties all 32 I/O channels.

- Programmable current load with dual commutating voltages

- Four Selectable output slew rates (0.2, 0.6, 0.9 and 1.2 V/ns typical)

- 50 Ohm output impedance

- Over-temperature detection/protection

- Over-voltage detection/protection

- Auxiliary channels (12):

- Eight LVTTL

- Four LVDS

Basic Elements of the DTI Module

As illustrated in Figure 1-1, the DTI module is comprised of the following major components; front panel, Digital Board, and a Driver/Receiver Board.

## **Front Panel**

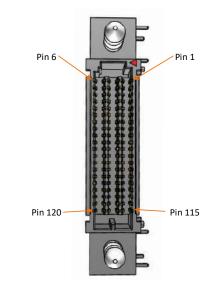

The front panel contains two connectors (J1 and P2) as well as two LEDs (LED1 and LED2). J1 contains all the I/O from the driver/receiver card. P2 links multiple DTIs together using the External Timing Bus boards. LED1 and LED2 provides module status information.

Figure 1-2 illustrates the front panel's connectors and LED indicators.

Figure 1-2 Front Panel Connectors and Indicators

## **Connectors**

The J1 connector contains all the digital I/O test signals

The P2 connector connects multiple DTI modules together using the ETB accessory boards.

## **LED Indicators**

| LED  | Indication                                                                                                   |

|------|--------------------------------------------------------------------------------------------------------------|

| LED1 | Red. Illuminated indicates module failure.                                                                   |

| LED2 | Green. Solid indicates FPGA loaded and<br>module initialized. Flashing indicates module<br>programming FPGA. |

Table 1-1 PXIe-2461 LED Indicators

## **Digital Board**

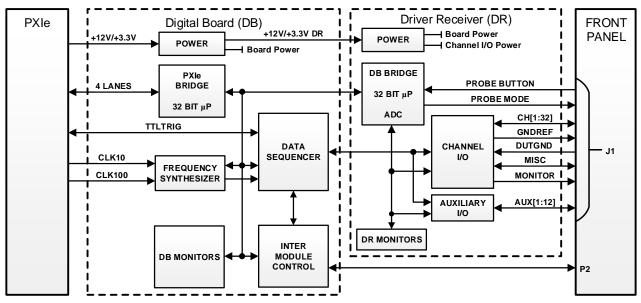

The digital board, hereafter referred to as DB, contains the connectors and headers required for routing signals to/from the PXIe backplane as well as the driver/receiver logic. The DB logic is comprised of the following major components.

## **DB Control**

This contains the logic to communicate and program DTI resources.

## PCI Express Bridge