# USB-6451 User Manual

2024-09-16

n

# Contents

| USB-6451 User Manual                                 | . 4 |

|------------------------------------------------------|-----|

| USB-6451 Overview                                    | . 5 |

| USB-6451 Driver Support                              | . 6 |

| Components of a USB-6451 System                      | . 7 |

| USB-6451 Theory of Operation                         | 10  |

| USB-6451 Block Diagram                               | 13  |

| USB-6451 Examples                                    | 17  |

| USB-6451 Front Panel                                 | 27  |

| USB-6451 Rear Panel                                  | 30  |

| USB-6451 Pinouts                                     | 32  |

| +5 V Power Source                                    | 42  |

| Analog Input Measurements                            | 43  |

| Analog Input Range                                   | 43  |

| Working Voltage Range                                | 44  |

| Analog Input Terminal Configurations                 | 45  |

| Dual-Channel Scanning Considerations                 | 47  |

| Analog Input Data Acquisition Methods                | 49  |

| Analog Input Signal Connections                      | 51  |

| Floating Signal Sources Connections                  | 53  |

| Ground-Referenced Signal Sources Connections         | 58  |

| Field Wiring Considerations for Analog Input Signals | 62  |

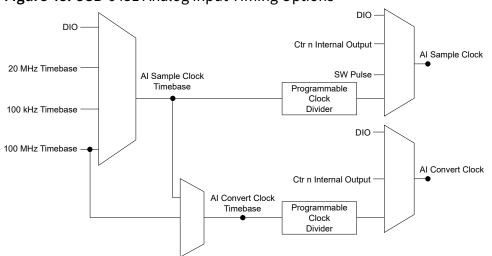

| Analog Input Timing Engine                           | 62  |

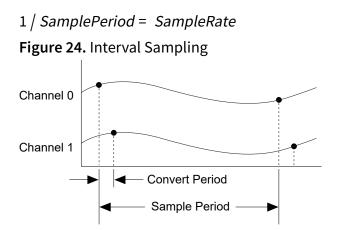

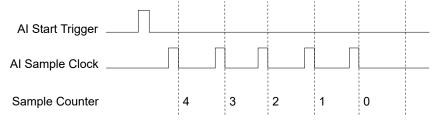

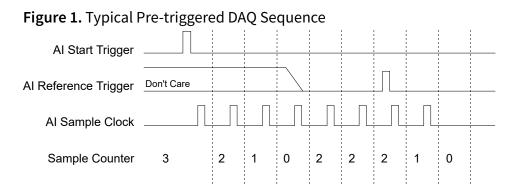

| Analog Input Timing Signals                          | 64  |

| Analog Output Measurements                           | 74  |

| Minimizing Glitches on the Output Signal             | 74  |

| Analog Output Data Generation Methods                | 74  |

| Analog Output Signal Connections                     | 76  |

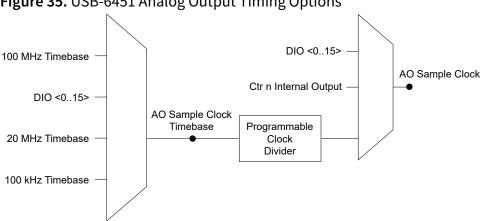

| Analog Output Timing Engine                          | 76  |

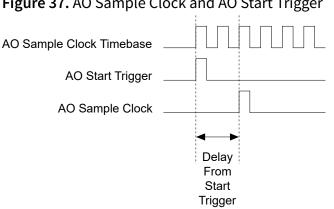

| Analog Output Timing Signals                         | 76  |

| Digital Input/Output Measurements                    | 81  |

| Digital Input Data Acquisition Methods               | 81  |

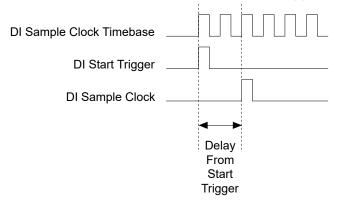

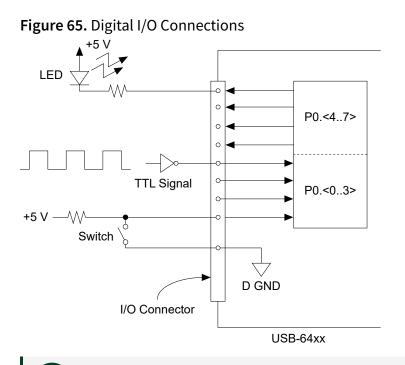

| Digital Input Timing Signals                         |     |

| Digital Output Data Generation Methods       86          | 6 |

|----------------------------------------------------------|---|

| Digital Output Timing Signals    88                      | 8 |

| I/O Protection                                           | 1 |

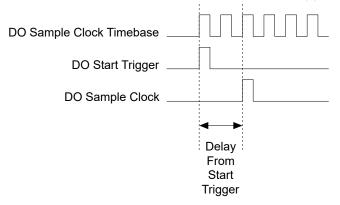

| DI Change Detection                                      | 2 |

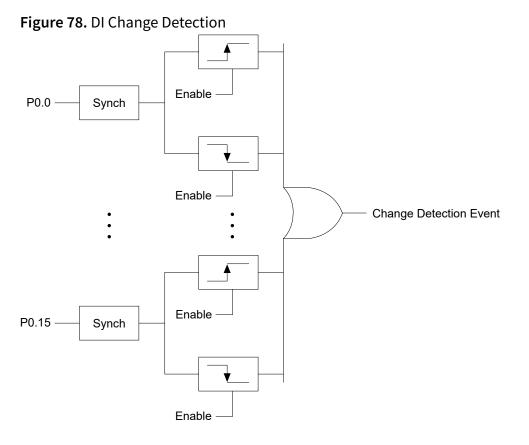

| Digital I/O Signal Connections                           | 3 |

| Using DIO Terminals as Timing Input Signals              | 4 |

| Using DIO Terminals to Export Timing Output Signals      | 5 |

| Counters                                                 | 6 |

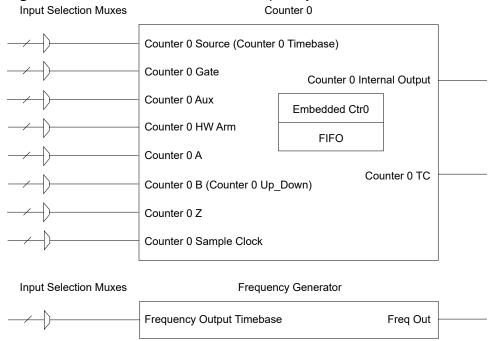

| Counter Timing Engine                                    | 7 |

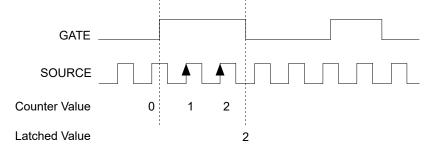

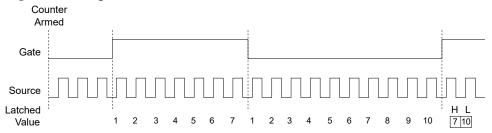

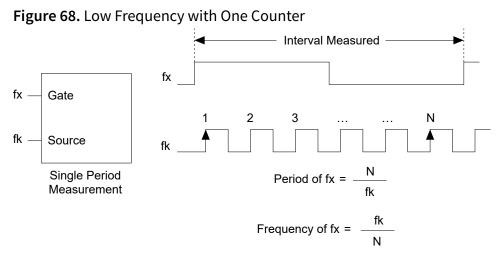

| Counter Input Applications    98                         | 8 |

| Counter Output Applications 112                          | 2 |

| Counter Timing Signals 119                               | 9 |

| Counter Triggering 124                                   | 4 |

| Cascading Counters                                       | 5 |

| Counter Signal Prescaling 125                            | 5 |

| Counter Signal Synchronization Modes 126                 | 6 |

| Installing the USB-6451 128                              | 8 |

| Unpacking the Kit                                        | 8 |

| Installing Software                                      | 8 |

| Wiring the USB-6451                                      | 9 |

| Verifying the Installation 129                           | 9 |

| Mounting the USB-6451 132                                | 2 |

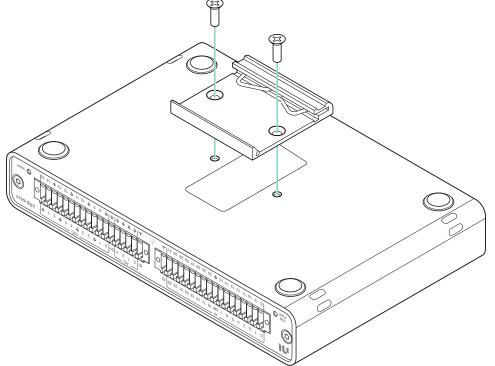

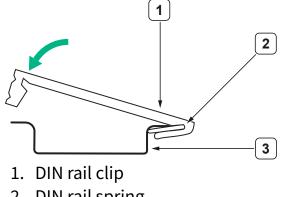

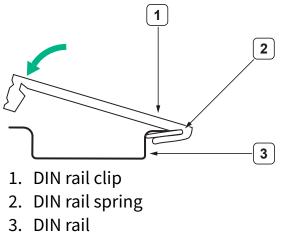

| Mounting the USB-6451 on a DIN Rail 132                  | 2 |

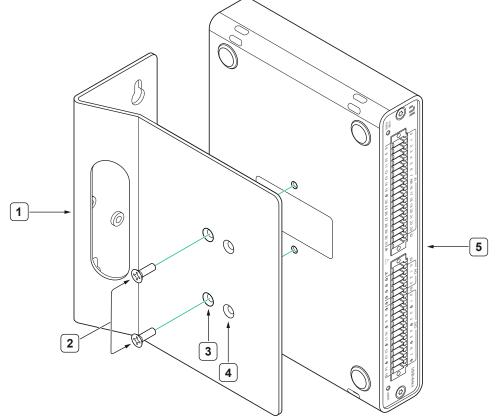

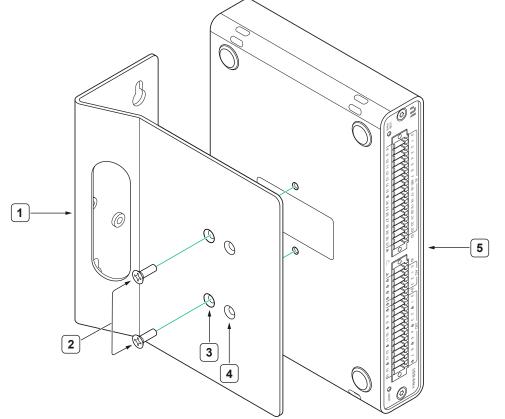

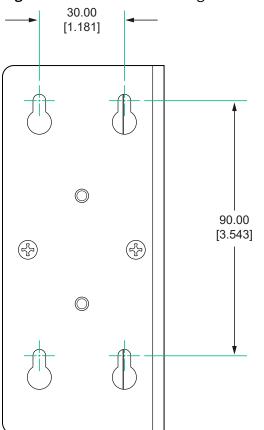

| Mounting the USB-6451 on a Wall or Panel 13 <sup>-</sup> | 7 |

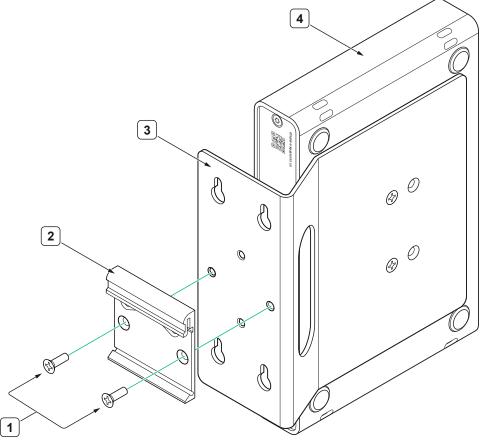

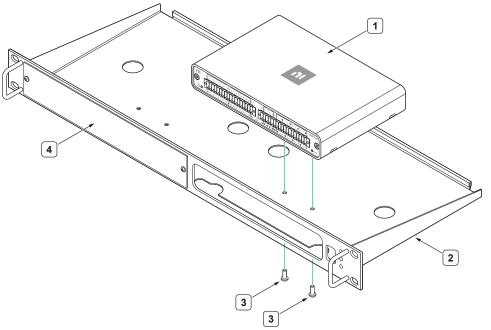

| Mounting the USB-6451 in a Rack 139                      | 9 |

| Mounting the USB-6451 with Zip Ties 140                  | 0 |

| Migrating from Previous Products 143                     | 3 |

# USB-6451 User Manual

The USB-6451 User Manual provides detailed descriptions of the product functionality and the step by step processes for use.

#### Looking for Something Else?

For information not found in the User Manual for your product, such as specifications and API reference, browse *Related Information*.

#### **Related information:**

- USB-6451 Specifications

- NI-DAQmx User Manual

- Software and Driver Downloads

- <u>Release Notes</u>

- License Setup and Activation

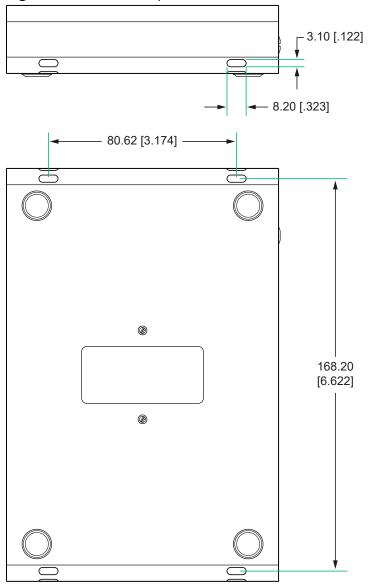

- Dimensional Drawings

- <u>Product Certifications</u>

- Letter of Volatility

- Discussion Forums

- NI Learning Center

# USB-6451 Overview

The USB-6451 is a multifunction Data Acquisition (DAQ) device featuring a combination of analog input, analog output, digital I/O, and counter/timers. Use the USB-6451 for a wide range of electromechanical test and measurement applications.

## **USB-6451 Key Features**

- 16 single-ended and 8 differential analog input channels

- Simultaneous sampling on up to 8 analog input channels

- 2 analog output channels

- 16 digital input/output channels

- 1 MS/s sampling rate on analog input

- 250 kS/s sampling rate on analog output channels

- 20-bit resolution on analog input channels

- 16-bit resolution on analog output channels

- 4 counters

- Compact and rugged enclosure with removable spring terminals for direct signal connection

- Multiple mounting options, including on a desktop, rack, DIN rail, or wall

# USB-6451 Driver Support

Determine the earliest driver version supported for your product.

Tip To optimize product performance, update to the most recent driver version.

#### Table 1. Earliest Driver Version Support

| Product  | Driver Name | Earliest Version Support |

|----------|-------------|--------------------------|

| USB-6451 | NI-DAQmx    | 2024 Q3.1                |

#### **Related tasks:**

• Installing Software

# Components of a USB-6451 System

The USB-6451 is designed for use in a system that may require hardware, drivers, and software to optimize USB-6451 for your application. Use the minimum required USB-6451 system components as a starting point for building your system.

| Component                                | Description and Recommendations                                                                                                                                                                                                                                                                       |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Computer                                 | The USB-6451 connects to a computer through USB for power and communication.                                                                                                                                                                                                                          |

| USB-6451                                 | Your USB DAQ device.                                                                                                                                                                                                                                                                                  |

| USB Cable                                | A USB cable connect your USB DAQ device to your computer.                                                                                                                                                                                                                                             |

| Mounting<br>Accessories                  | <ul> <li>The USB-6451 supports a number of mounting configurations including:</li> <li>Resting on a flat surface, unmounted</li> <li>Mounting to a DIN rail, wall, or panel</li> <li>Mounting in a rack</li> <li>Securing in place with zip ties</li> </ul>                                           |

| Backshells<br>for<br>Connector<br>Blocks | You can install backshells over the spring-terminal connector blocks to protect the wiring and provide strain relief. The USB-6451 shipping kit includes backshells, but you can order more separately.                                                                                               |

| NI-DAQmx                                 | Instrument driver software that provides functions to interact with the USB-6451 and execute measurements using the USB-6451.                                                                                                                                                                         |

|                                          | <b>Note</b> For optimal performance, use the most current version of NI-<br>DAQmx with the USB-6451.                                                                                                                                                                                                  |

| NI<br>Applications                       | <ul> <li>NI-DAQmx offers driver support for the following applications:</li> <li>LabVIEW</li> <li>LabVIEW Real-Time Module</li> <li>FlexLogger</li> <li>LabWindows/CVI</li> <li>LabWindows/CVI Real-Time Module</li> <li>NI-DAQmx Measurement Studio Integration (Measurement Studio 2019)</li> </ul> |

Table 2. Minimum Required USB-6451 System Components

| Component | Description and Recommendations                         |

|-----------|---------------------------------------------------------|

|           | <ul> <li>C/C++</li> <li>.NET</li> <li>Python</li> </ul> |

## Part Numbers for Recommended Accessories

Use part numbers to purchase the cables and accessories NI recommends to optimize the performance of the USB-6451.

| Accessory                                                   | Description                                                                                                                                                               | Part Number |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| USB-64xx Mounting Kit for DIN<br>Rail                       | Use to mount the USB-6451 on a DIN rail horizontally.                                                                                                                     | 789986-01   |

| USB-64xx Mounting Kit for DIN<br>Rail, Wall, or Panel Mount | Use to mount the USB-6451 on<br>a DIN rail vertically or to mount<br>it on a wall or a panel. Includes<br>a right-angle USB Type-C cable<br>for mounting close to a wall. | 789955-01   |

| USB-64xx Rack Mount Shelf                                   | Use to mount up to two<br>USB-6451 in a 19-in. rack. Uses<br>1U of rack height. Includes two<br>right-angle, 2 m USB Type-C<br>cables.                                    | 789953-01   |

| Spring-terminal connector                                   | Use to wire the USB-6451.                                                                                                                                                 | 785502-01   |

| Backshell for spring-terminal connector                     | Use to protect the wiring and provide strain relief.                                                                                                                      | 785080-01   |

| Type-C USB 3.0 Male to Type-C<br>USB 3.0 Male USB Cable     | Use to connect the USB-6451 to<br>a computer. One end of the<br>cable has a locking thumb<br>screw for securing the cable to<br>the USB-6451.                             | 789956-02   |

Table 3. Part Numbers for Recommended Accessories

#### Additional Cabling and Accessory Guidance

NI recommends the following:

• Using individually shielded, twisted-pair wires that are 2 m or less to connect AI signals to the USB-6451.

#### **Related tasks:**

- Mounting the USB-6451 on a DIN Rail

- Mounting the USB-6451 on a Wall or Panel

- Mounting the USB-6451 in a Rack

# USB-6451 Theory of Operation

The USB-6451 is a simultaneously-sampled multifunction I/O Data Acquisition (DAQ) device that connects to a computer via a USB Type-C interface. This single USB Type-C cable provides power as well as USB 3.0 SuperSpeed communication.

#### **NI Signal Streaming**

NI signal streaming technology performs the USB communication. NI signal streaming technology allows for efficient, high-speed, bidirectional data streaming to and from the host computer. NI signal streaming uses USB bandwidth efficiently to support data transfer from the different analog input, analog output, and digital I/O subsystems on the USB-6451.

#### **Analog Input**

The USB-6451 analog input provides 16 single-ended or 8 differential input channels that are connected to 8 simultaneously-sampled, 20-bit ADCs. Each differential channel pair has its own programmable gain instrumentation amplifier, multiplexers, and ADC. This design enables high-speed simultaneous sampling of all differential channels up to the maximum rate of 1 MS/s on all channels. Multiplexers allow you to sample the differential input pair as two separate single-ended channels for additional flexibility. In this single-ended mode, the maximum sample rate drops to 500 kS/s on all channels.

The maximum input range of ±10 V is suitable for connecting to a wide variety of electronics or sensors with conditioned outputs. A programmable gain instrumentation amplifier with four different ranges delivers a scaled signal to the 20-bit ADC to maximize resolution for lower voltage signals.

An accurate, low-drift onboard reference plus integrated self-calibration circuitry ensures that the 16 single-ended or 8 differential performs accurately across time and temperature.

### Analog Output

The analog output circuitry consists of two independent 16-bit, ±10 V analog outputs. You can use these outputs for stimulus or simple control. You can also make singlepoint updates or generate waveforms.

#### Digital I/O, Counters, and Timers

The USB-6451 has 16 digital I/O lines. You can configure each line as input or output individually. You can use the digital I/O lines for either single-point updates or high-speed waveform input/output.

The USB-6451 also has four 32-bit counters that you can route to the digital I/O lines. These counters can count events, measure frequency, measure using an incremental encoder, generate frequency, generate a pulse train, and more.

Flexible routing allows you to route any counter to any of the digital I/O lines.

### Timing, Triggering, and Synchronization

Independent timing engines control how each device subsystem operates. This functionality allows the subsystems to either run independently or synchronously.

You can route timing and trigger signals to or from the digital I/O lines to synchronize with other equipment or DAQ devices. The timing and trigger signals include signals such as a Start Trigger to control when an operation starts or a Sample Clock, which toggles each time a sample is acquired.

### **Enclosure and Connectivity**

All this functionality is housed in a rugged metal enclosure. You can use the enclosure as-is on a desk or mount it to equipment with built-in zip-tie mounting slots. Optional DIN rail, wall-mount, and rack-mount kits are available for mounting in other environments.

I/O connections are made through removable spring-terminal connectors. These connector blocks use push-in technology that enables you to wire of input signals

rapidly. You can use the included backshells to protect the wiring and provide strain relief.

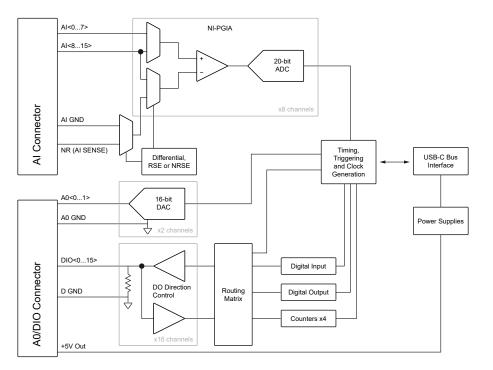

# USB-6451 Block Diagram

Use the USB-6451 block diagram to learn more about the different analog input, analog output, and digital I/O subsystems of the USB-6451 work together.

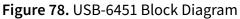

## **Analog Input Block Diagram**

The following figure shows the analog input circuitry of the USB-6451.

Every differential channel pair has its own instrumentation amplifier, multiplexers, and ADC. This allows high-speed simultaneous sampling of all differential channels up to the maximum rate of 1 MS/s on all channels. For additional flexibility, multiplexers allow sampling the differential input pair as 2 separate single-ended channels. In this single-ended mode, the maximum sample rate drops to 500 kS/s on all channels.

#### Figure 1. USB-6451 Analog Input Block Diagram

- I/O Connector—You can connect analog input signals to the USB-6451 through the I/O connector.

- AI Terminal Configuration—These multiplexers configure the input mode to either differential, referenced single-ended (RSE), or non-referenced single-ended (NRSE).

- Instrumentation Amplifier (NI-PGIA)—The NI programmable gain instrumentation amplifier (NI-PGIA) can amplify or attenuate an AI signal to ensure that you get the maximum resolution of the ADC. The NI-PGIA also allows you to select the input range.

- ADC—The analog-to-digital converter (ADC) digitizes the AI signal by converting the analog voltage into a digital number.

- Analog Input Timing Signals—For information about the analog input timing signals available on USB-6451 devices, refer to the *Analog Input Timing Signals* section.

- AI FIFO—The USB-6451 can perform both single and multiple A/D conversions of a fixed or infinite number of samples. A large first-in-first-out (FIFO) buffer holds data during A/D conversions to ensure that no data is lost. The USB-6451 can handle multiple A/D conversion operations with DMA or programmed I/O.

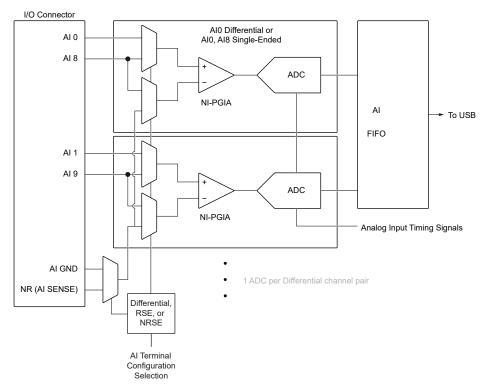

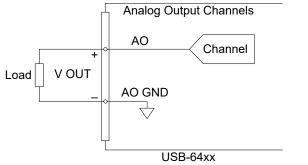

## Analog Output Block Diagram

The USB-6451 has two voltage output channels capable of either software-timed single-point updates or hardware-timed waveform generation.

Figure 81. USB-6451 Analog Output Block Diagram

The main blocks featured in the USB-6451 analog output circuitry are as follows:

- Digital-to-analog converters (DACs)—Convert digital codes to analog voltages.

- AO FIFO—Enables analog output waveform generation. It is a first-in-first-out (FIFO) memory buffer between the computer and the DACs. It allows you to either stream a waveform with new data continuously provided from USB or download an entire waveform to the USB-6451 where it can be regenerated entirely from the onboard buffer.

- **AO Sample Clock**—Reads a sample from the AO FIFO and generates the AO voltage.

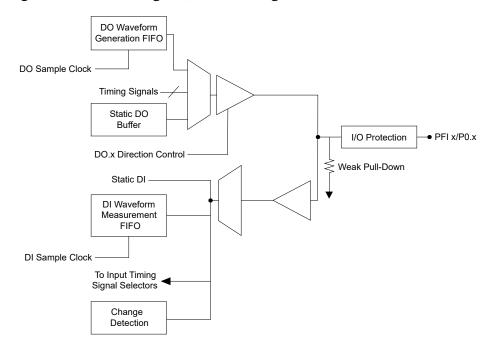

## Digital I/O Block Diagram

The USB-6451 has 16 bidirectional digital I/O signals that are grouped together in software as a single port referred to as Port 0.

These signals can function as digital I/O as well as counter, timer, or triggering I/O. When used as counter, timer, or triggering I/O, the lines are referred to as **Programmable Function Interface (PFI)** lines. The digital I/O lines on the USB-6451 support the following features:

- Direction and function of each terminal individually controllable

- Static digital input and output

- High-speed digital waveform generation

- High-speed digital waveform acquisition

- Digital input change detection trigger/interrupt

- Timing input signal for analog input, analog output, digital input, digital output, or counter/timer functions

- Timing output signal from analog input, analog output, digital input, digital output, or counter/timer functions

The following figure shows the circuitry of one digital I/O line. Each digital I/O line is similar.

Figure 4. USB-6451 Digital I/O Block Diagram

In software, these channels are referred to as port0/line0:15 when used as digital I/O and PFI 0:15 when used for other purposes, such as timing I/O.

# USB-6451 Examples

NI installs example code with your software or driver that demonstrates the functionality of USB-6451. Use these examples to learn about the product or accelerate your own application development.

Most NI products install examples that you can access directly or from within NI software. The example experience can differ slightly across products and versions.

#### LabVIEW Examples

USB-6451 LabVIEW examples are located in the %ProgramFiles%\NI\LVAddons\ nidaqmx\1\examples\NI-DAQmx directory.

| Example Name                             | Description                                                                                                                                                                                                        |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Voltage (with Events) - Continuous Input | Demonstrates how to continuously acquire<br>buffered voltage measurements. It uses software<br>events to ensure that the program does not<br>become unresponsive while waiting for samples<br>to become available. |

| Voltage - Continuous Input               | Demonstrates how to continuously acquire voltage measurement.                                                                                                                                                      |

| Voltage - Finite Input                   | Demonstrates how to acquire a single buffer of voltage measurements.                                                                                                                                               |

| Voltage - SW-Timed Input                 | Demonstrates how to acquire a voltage based off of software timing.                                                                                                                                                |

| Voltage - Continuous Output              | Demonstrates how to continuously re-generate<br>analog output data from a buffer in your<br>computer's memory.                                                                                                     |

| Voltage - Finite Output                  | Demonstrates how to output a voltage based on<br>a finite amount of data from a buffer in your<br>computer's memory.                                                                                               |

| Voltage - On Demand Output               | Demonstrates how to generate a user-defined voltage using the analog output.                                                                                                                                       |

Table 4. Common USB-6451 LabVIEW Examples

| Example Name                                                  | Description                                                                                                                                                                             |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Counter - Count Edges                                         | Demonstrates how to continuously read back<br>the number of digital edges that have been<br>counted by a counter input.                                                                 |

| Counter - Read Encoder                                        | Demonstrates how to use a counter to continually monitor the angular position of an encoder.                                                                                            |

| Counter - Read Pulse Duty Cycle and Frequency<br>(Continuous) | Demonstrates how to configure a pulse<br>measurement to acquire frequency and duty<br>cycle based off of an external clock.                                                             |

| Counter - Continuous Output                                   | Demonstrates how to continuously generate digital pulses using a counter output.                                                                                                        |

| Counter - Finite Output                                       | Demonstrates how to generate a finite number<br>of digital pulses using a counter output. On<br>some hardware, this requires the use of a second<br>counter to generate a gate signal.  |

| Counter - Single Pulse Output                                 | Demonstrates how to generate a single pulse<br>using a counter output. The single pulse may be<br>triggered once or repeatedly from an external<br>source.                              |

| Digital - Change Detection                                    | Demonstrates how to acquire a continuous<br>amount of digital data based off of the changes<br>of an external signal across one or many lines on<br>either the rising or falling edges. |

| Digital - Continuous Input                                    | Demonstrates how to acquire a continuous<br>amount of digital data based off of a sample<br>clock.                                                                                      |

| Digital - SW-Timed Input                                      | Demonstrates how to acquire the state of digital lines based off of software timing.                                                                                                    |

| Digital - Continuous Output                                   | This example Demonstrates how to generate a continuous amount of digital data based off of a sample clock.                                                                              |

| Digital - Finite Output                                       | Demonstrates how to generate a finite amount of digital data based off of a sample clock.                                                                                               |

| Digital - SW-Timed Output                                     | Demonstrates how to generate digital output data using software timing.                                                                                                                 |

### Python Examples in

USB-6451 Python examples are located in GitHub at github.com/ni/nidaqmxpython/tree/master/examples.

| Example Name                                                    | Description                                                                                                                                                                                                                        |

|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| analog_in/cont_voltage_acq_int_clk.py                           | Demonstrates how<br>to acquire a<br>continuous amount<br>of data using the<br>USB-6451's internal<br>clock.                                                                                                                        |

| analog_in/<br>cont_voltage_acq_int_clk_every_n_samples_event.py | Demonstrates how<br>to use Every N<br>Samples events to<br>acquire a continuous<br>amount of data<br>using the USB-6451's<br>internal clock. The<br>Every N Samples<br>events indicate when<br>data is available<br>from NI-DAQmx. |

| analog_in/voltage_acq_int_clk.py                                | Demonstrates how<br>to acquire a finite<br>amount of DATA<br>using the USB-6451's<br>internal clock.                                                                                                                               |

| analog_in/voltage_sample.py                                     | Demonstrates how<br>to acquire a voltage<br>measurement using<br>software timing.                                                                                                                                                  |

| analog_out/cont_gen_voltage_wfm_int_clk.py                      | Demonstrates how<br>to output a<br>continuous periodic<br>waveform using an<br>internal sample<br>clock.                                                                                                                           |

| Example Name                                                                 | Description                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>analog_out/ cont_gen_voltage_wfm_int_clk_every_n_samples_event.py</pre> | Demonstrates how<br>to use a Every N<br>Samples events to<br>output a continuous<br>periodic waveform<br>to an Analog Output<br>Channel using an<br>internal sample<br>clock. The Every N<br>Samples events<br>indicate when the<br>specified number of<br>samples generation<br>is complete. |

| analog_out/gen_voltage_wfm_int_clk.py                                        | Demonstrates how<br>to output a finite<br>number of voltage<br>samples to an<br>Analog Output<br>Channel using an<br>internal sample<br>clock.                                                                                                                                                |

| analog_out/voltage_update.py                                                 | Demonstrates how<br>to output a single<br>Voltage Update<br>(Sample) to an<br>Analog Output<br>Channel.                                                                                                                                                                                       |

| counter_in/cnt_dig_event.py                                                  | Demonstrates how<br>to count digital<br>events on a Counter<br>Input Channel. You<br>can configure the<br>Initial Count, Count<br>Direction, and Edge.                                                                                                                                        |

| counter_in/read_pulse_freq.py                                                | Demonstrates how<br>to configure a pulse<br>measurement to<br>acquire frequency                                                                                                                                                                                                               |

| Example Name                             | Description                                                                                                                                                                          |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          | and duty cycle.                                                                                                                                                                      |

| counter_out/cont_gen_dig_pulse_train.py  | Demonstrates how<br>to generate a<br>continuous digital<br>pulse train from a<br>Counter Output<br>Channel. You can<br>configure the<br>Frequency, Duty<br>Cycle, and Idle State.    |

| counter_out/write_single_dig_pulse.py    | Demonstrates how<br>to generate a single<br>digital pulse from a<br>Counter Output<br>Channel. You can<br>configure the Initial<br>Delay, High Time,<br>Low Time, and Idle<br>State. |

| digital_in/acq_dig_port_int_clk.py       | Demonstrates how<br>to input a finite<br>digital pattern using<br>the USB-6451's<br>internal clock.                                                                                  |

| digital_in/cont_acq_dig_lines_int_clk.py | Demonstrates how<br>to acquire a<br>continuous digital<br>waveform using the<br>USB-6451's internal<br>clock.                                                                        |

| digital_in/read_dig_lines.py             | Demonstrates how<br>to read values from<br>one or more digital<br>input channels.                                                                                                    |

| digital_in/read_dig_port.py              | Demonstrates how<br>to read values from a<br>digital input port.                                                                                                                     |

| digital_out/cont_gen_dig_port_int_clk.py | Demonstrates how                                                                                                                                                                     |

| Example Name                        | Description                                                                                           |

|-------------------------------------|-------------------------------------------------------------------------------------------------------|

|                                     | to output a<br>continuous digital<br>pattern using the<br>USB-6451's clock.                           |

| digital_out/gen_dig_line_int_clk.py | Demonstrates how<br>to output a finite<br>digital waveform<br>using the USB-6451's<br>internal clock. |

| digital_out/write_dig_lines.py      | Demonstrates how<br>to write values to a<br>digital output<br>channel.                                |

| digital_out/write_dig_port.py       | Demonstrates how<br>to write values to a<br>digital output port.                                      |

| system_properties.py                | Demonstrates how<br>to use system<br>properties in NI-<br>DAQmx.                                      |

#### .NET Examples

USB-6451 examples in .NET are located in the Users\Public\Public Documents\National Instruments\NI-DAQ\Examples\... directory.

Table 6. Common USB-6451 .NET Examples

| Example Name                                                                                         | Description                                                                                  |  |

|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|

| Analog In\Measure Voltage\<br>AcqMultVoltageSamples_SWTimed\CS\<br>AcqMultVoltageSamples_SWTimed.sln | Demonstrates how to acquire a finite amount of data using a software timer.                  |  |

| Analog In\Measure Voltage\<br>AcqOneVoltageSample\CS\<br>AcqOneVoltageSample.sln                     | Demonstrates how to acquire a single<br>reading from a constant or slowly varying<br>signal. |  |

| Analog In\Measure Voltage\                                                                           | Demonstrates how to acquire a finite                                                         |  |

| Example Name                                                                                                        | Description                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AcqVoltageSamples_IntClk\CS\<br>AcqVoltageSamples_IntClk.sln                                                        | amount of data using an internal clock.                                                                                                                                                                                                                                                                                                                                                   |

| Analog In\Measure Voltage\<br>ContAcqVoltageSamples_IntClk\CS\<br>ContAcqVoltageSamples_IntClk.sln                  | Demonstrates how to acquire a continuous amount of data using the USB-6451's internal clock.                                                                                                                                                                                                                                                                                              |

| Analog In\Measure Voltage\<br>ContAcqVoltageSamples_SWTimed\CS\<br>ContAcqVoltageSamples_SWTimed.sln                | Demonstrates how to acquire a continuous amount of data using a software timer.                                                                                                                                                                                                                                                                                                           |

| Analog Out\Generate Voltage\<br>ContGenVoltageWfm_IntClk\CS\<br>ContGenVoltageWfm_IntClk.sln                        | Demonstrates how to continuously<br>output a periodic waveform using an<br>internal sample clock.                                                                                                                                                                                                                                                                                         |

| Analog Out\Generate Voltage\<br>GenMultVoltUpdates_IntClk\CS\<br>GenMultVoltUpdates_IntClk.sln                      | Demonstrates how to output multiple<br>voltage updates (samples) to an analog<br>output channel.                                                                                                                                                                                                                                                                                          |

| Analog Out\Generate Voltage\<br>GenMultVoltUpdates_SWTimed\CS\<br>GenMultVoltUpdates_SWTimed.sln                    | Demonstrates how to output multiple<br>voltage updates (samples) to an analog<br>output channel in a software timed loop.                                                                                                                                                                                                                                                                 |

| Analog Out\Generate Voltage\<br>GenVoltageUpdate\CS\<br>GenVoltageUpdate.sln                                        | Demonstrates how to output a single<br>voltage update (sample) to an analog<br>output channel.                                                                                                                                                                                                                                                                                            |

| Counter\Count Digital Events\<br>CountDigEvents\CS\CountDigEvents.sln                                               | Demonstrates how to count digital<br>events on a Counter Input Channel. You<br>can configure the Initial Count, Count<br>Direction, and Edge. This example shows<br>how to count edges on the counter's<br>default source pin, but you could easily<br>expand it to count edges on any PFI,<br>RTSI, or internal signal.                                                                  |

| Counter\Count Digital Events\<br>CountDigEventsBuffContinuous_ExtClk\CS\<br>CountDigEventsBuffContinuous_ExtClk.sln | Demonstrates how to count buffered<br>digital events on a Counter Input<br>channel. You can configure the initial<br>count, count direction, edge, and sample<br>clock source. Edges are counted on the<br>counter's default input terminal, but you<br>could easily modify it to count edges on a<br>PFI or RTSI line. Note: For buffered event<br>counting, an external sample clock is |

| Example Name                                                                                  | Description                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                               | necessary to signal when a sample<br>should be inserted into the buffer.<br>Specify the source terminal of the<br>external clock in the clock source text<br>box when you run the example.                                                                                                                                                                       |

| Counter\Generate Pulse\GenDigPulse\CS\<br>GenDigPulse.sln                                     | Demonstrates how to generate a single<br>digital pulse from a counter output<br>channel. You can configure the initial<br>delay, high time, low time, and idle state<br>in software. This example shows how to<br>configure the pulse in terms of time, but<br>you can easily modify it to generate a<br>pulse in terms of frequency and duty<br>cycle or ticks. |

| Counter\Generate Pulse\<br>GenDigPulseTrain_Continuous\CS\<br>GenDigPulseTrain_Continuous.sln | Demonstrates how to generate a<br>continuous digital pulse train from a<br>counter output channel. You can<br>configure the frequency, duty cycle, and<br>idle state. This example shows how to<br>configure the pulse in terms of frequency<br>and duty cycle, but you can easily modify<br>it to generate a pulse in terms of time or<br>ticks.                |

| Digital\Generate Values\WriteDigChan\<br>CS\WriteDigChan.sln                                  | Demonstrates how to write values to a digital output channel.                                                                                                                                                                                                                                                                                                    |

| Digital\Generate Values\WriteDigPort\<br>CS\WriteDigPort.sln                                  | Demonstrates how to write values to a digital output port.                                                                                                                                                                                                                                                                                                       |

| Digital\Read Values\ReadDigChan\CS\<br>ReadDigChan.sln                                        | Demonstrates how to read values from one or more digital input channels.                                                                                                                                                                                                                                                                                         |

| Digital\Read Values\ReadDigPort\CS\<br>ReadDigPort.sln                                        | Demonstrates how to read a single value from a digital port.                                                                                                                                                                                                                                                                                                     |

## Browsing and Searching for Examples in NI Example Finder

Use NI Example Finder to browse and to search for examples.

You can use NI Example Finder to find examples for the following products.

- LabVIEW

- LabWindows/CVI

- NI drivers accessible from LabVIEW

- NI drivers accessible from LabWindows/CVI

- 1. Launch LabVIEW or LabWindows/CVI.

- 2. Open NI Example Finder.

| Option         | Description                                                               |

|----------------|---------------------------------------------------------------------------|

| LabVIEW        | Select Help <u>»</u> Find Examples. from the menu bar.                    |

| LabWindows/CVI | Click <b>Find Examples</b> from the Examples section of the Welcome Page. |

NI Example Finder launches.

- 3. Optional: Configure NI Example Finder for LabWindows/CVI.

- a. Click Setup. Configure Example Finder opens.

- b. In Configure Example Finder, click **Software**, then select LabWindows/CVI, and click **OK**.

NI Example Finder updates with all the examples for LabWindows/CVI.

4. Search the example VIs for your product.

| Option                | Description                                                                                                                                                                                                                                                                         |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Click the Browse tab. | Choose <b>Browse</b> when you want to drill down through folders to find examples organized by task category.                                                                                                                                                                       |  |

|                       | <b>Tip</b> Examples installed with NI<br>drivers or third-party drivers are<br>often found within the <b>Hardware</b><br><b>Input and Output</b> folder. Examples<br>installed with toolkits or modules<br>are often found within the <b>Toolkits</b><br><b>and Modules</b> folder. |  |

| Click the Search tab. | Choose <b>Search</b> when you want to find<br>examples by searching for topics, products, or<br>modules relevant to your application.                                                                                                                                               |  |

5. To open an example, double-click the folder or the example.

Tip You can modify an example VI to fit your application. You can also copy and paste from one or more examples into a VI that you create.

# USB-6451 Front Panel

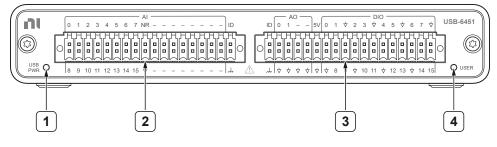

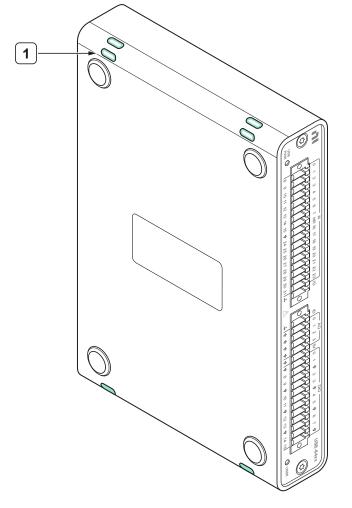

Use the front panel to identify the connectors and LEDs of the USB-6451.

#### Figure 78. USB-6451 Front Panel

- 1. USB PWR LED

- 2. Al connector

- 3. AO/DIO connector

- 4. USER LED

#### **USB PWR LED**

The USB PWR LED indicates the power status and communication activity.

| Color | Pattern  | Meaning                                                                                    |  |

|-------|----------|--------------------------------------------------------------------------------------------|--|

| Off   | _        | The USB-6451 is not powered or not ready                                                   |  |

| Green | Solid    | The USB-6451 is powered and<br>ready but not actively<br>communicating with the host<br>PC |  |

|       | Blinking | USB-6451 is powered on and actively communicating with the host PC                         |  |

Table 7. USB-6451 USB PWR LED Indicator Status

#### Why Is the USB PWR LED Off?

The USB PWR LED remains off when the USB-6451 is not powered or ready for operation.

This could be caused by the following reasons:

- The USB cable is not connected.

- The upstream PC or hub is not connected.

- The PC has put the USB-6451 into a low-power suspend or sleep state.

- The PC does not have a version of NI-DAQmx installed that supports the USB-6451.

- The USB-6451 is busy updating firmware.

**Note** When you connect the USB-6451 to a computer that has a different version of NI-DAQmx installed than the computer that the USB-6451 was connected to previously, NI-DAQmx checks to see if the USB-6451 requires a firmware update. If it does, the USB-6451 automatically updates the firmware. This update may take several minutes. During this time, the LED will remain off until the USB-6451 is ready. Leave the USB-6451 connected to the computer during this time.

### **AI Connector**

Provides pins for Analog Input signal connections.

#### **Related reference:**

• USB-6451 AI Connector Pinout

### **AO/DIO Connector**

Provides pins for analog output and digital I/O signal connections.

#### **Related reference:**

USB-6451 AO/DIO Connector Pinout

## **USER LED**

This feature is not supported yet, but support will be added in the future.

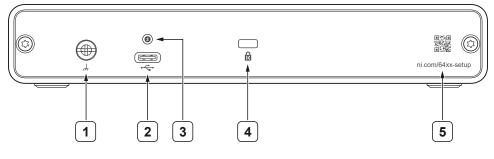

# USB-6451 Rear Panel

Use the rear panel to identify the features and connectors of the USB-6451.

Figure 78. USB-6451

- 1. Chassis ground lug

- 2. USB Type-C connector

- 3. USB Type-C jack socket

- 4. Security lock slot

- 5. Setup QR code

## **Chassis Ground Lug**

Use the chassis ground lug to connect the USB-6451 to earth ground. Ensure this screw is always attached during operation because it also secures the USB connector.

## **USB Type-C Connector**

Use the USB Type-C connector to connect the USB-6451 to a host computer through a USB Type-C cable.

## **Security Lock**

Insert a security cable to secure the USB-6451.

## Setup QR Code

Use the QR code on the USB-6451 to access the setup page. You can also access the

setup page by going to ni.com/64xx-setup.

# USB-6451 Pinouts

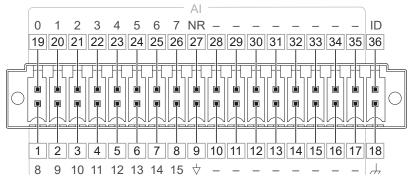

## **USB-6451 AI Connector Pinout**

Use the pinout to connect to analog input terminals on the USB-6451.

#### Figure 58. USB-6451 AI Connector Pinout

#### Table 8. USB-6451 AI Connector Pin Assignments

| Pin | Signal     |

|-----|------------|

| 1   | AI 8       |

| 2   | AI 9       |

| 3   | AI 10      |

| 4   | AI 11      |

| 5   | AI 12      |

| 6   | AI 13      |

| 7   | AI 14      |

| 8   | AI 15      |

| 9   | AI GND     |

| 10  | No connect |

| 11  | No connect |

| 12  | No connect |

| 13  | No connect |

| 14  | No connect |

| Pin | Signal        |  |

|-----|---------------|--|

| 15  | No connect    |  |

| 16  | No connect    |  |

| 17  | No connect    |  |

| 18  | CHSGND        |  |

| 19  | AI 0          |  |

| 20  | AI 1          |  |

| 21  | AI 2          |  |

| 22  | AI 3          |  |

| 23  | AI 4          |  |

| 24  | AI 5          |  |

| 25  | AI 6          |  |

| 26  | AI 7          |  |

| 27  | NR (AI SENSE) |  |

| 28  | No connect    |  |

| 29  | No connect    |  |

| 30  | No connect    |  |

| 31  | No connect    |  |

| 32  | No connect    |  |

| 33  | No connect    |  |

| 34  | No connect    |  |

| 35  | No connect    |  |

| 36  | ID 0          |  |

#### Table 9. USB-6451 AI Connector Signal Descriptions

| Signal  | Function                 | Reference | Direction | Description                 |

|---------|--------------------------|-----------|-----------|-----------------------------|

| AI <07> | Analog input<br>channels | Varies    | Input     | Supports<br>differential or |

| Signal   | Function                 | Reference | Direction | Description                                                                                                                                                                                                                                                                                                         |

|----------|--------------------------|-----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                          |           |           | configure<br>the input<br>mode<br>per<br>channel.                                                                                                                                                                                                                                                                   |

| AI <815> | Analog input<br>channels | Varies    | Input     | Supports single-<br>ended<br>measurements only.<br>The default<br>configuration is RSE<br>mode. In RSE mode,<br>AI GND is the<br>reference for the<br>voltage<br>measurement. In<br>NRSE mode, the NR<br>pin is the reference.<br>For differential<br>measurements,<br>refer to the<br>descriptions for AI<br><07>. |

| AI GND   | Analog input<br>ground   |           |           | The reference point<br>for single-ended<br>measurements in<br>RSE mode and the<br>bias current return<br>point for differential<br>measurements.<br>AI GND, AO GND, D<br>GND, and CHSGND<br>are all connected<br>internally.                                                                                        |

| Signal        | Function                  | Reference | Direction | Description                                                                                                                                                                                                                                                                   |

|---------------|---------------------------|-----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NR (AI SENSE) | AI SENSE for<br>NRSE mode |           | Input     | The AI SENSE pin is<br>labeled "NR"<br>because it is used<br>when the input<br>terminal is<br>configured to NRSE<br>mode. In NRSE<br>mode, AI SENSE<br>acts as a remote<br>sense of a reference<br>voltage that can be<br>at a different<br>voltage potential<br>than AI GND. |

| CHSGND        | Chassis ground            |           |           | Connects directly to<br>the chassis ground<br>of the USB-6451<br>enclosure. It can be<br>used as a<br>termination point<br>for shielded cables<br>to help improve<br>measurement<br>quality.                                                                                  |

| ID 0          | _                         | _         | _         | This feature is not supported yet.                                                                                                                                                                                                                                            |

#### **Related reference:**

<u>Analog Input Terminal Configurations</u>

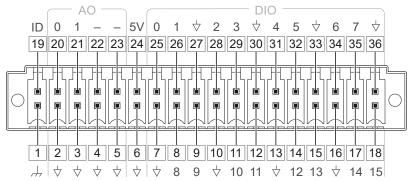

## USB-6451 AO/DIO Connector Pinout

Use the pinout to connect to analog output and digital input/output terminals on the USB-6451.

#### Figure 69. USB-6451 AO/DIO Connector Pinout

#### Table 10. USB-6451 AO/DIO Connector Pin Assignments

| Pin | Signal                      |

|-----|-----------------------------|

| 1   | CHSGND                      |

| 2   | AO GND                      |

| 3   | AO GND                      |

| 4   | AO GND                      |

| 5   | AO GND                      |

| 6   | D GND                       |

| 7   | D GND                       |

| 8   | PFI 8/P0.8 (port0/line8)    |

| 9   | PFI 9/P0.9 (port0/line9)    |

| 10  | D GND                       |

| 11  | PFI 10/P0.10 (port0/line10) |

| 12  | PFI 11/P0.11 (port0/line11) |

| 13  | D GND                       |

| 14  | PFI 12/P0.12 (port0/line12) |

| 15  | PFI 13/P0.13 (port0/line13) |

| 16  | D GND                       |

| 17  | PFI 14/P0.14 (port0/line14) |

| 18  | PFI 15/P0.15 (port0/line15) |

| 19  | ID 1                        |

| Pin | Signal                   |

|-----|--------------------------|

| 20  | AO 0                     |

| 21  | AO 1                     |

| 22  | No connect               |

| 23  | No connect               |

| 24  | +5 V                     |

| 25  | PFI 0/P0.0 (port0/line0) |

| 26  | PFI 1/P0.1 (port0/line1) |

| 27  | D GND                    |

| 28  | PFI 2/P0.2 (port0/line2) |

| 29  | PFI 3/P0.3 (port0/line3) |

| 30  | D GND                    |

| 31  | PFI 4/P0.4 (port0/line4) |

| 32  | PFI 5/P0.5 (port0/line5) |

| 33  | D GND                    |

| 34  | PFI 6/P0.6 (port0/line6) |

| 35  | PFI 7/P0.7 (port0/line7) |

| 36  | D GND                    |

#### Table 11. USB-6451 AO/DIO Connector Signal Descriptions

| Signal  | Function                  | Reference | Direction | Description                                                                                           |

|---------|---------------------------|-----------|-----------|-------------------------------------------------------------------------------------------------------|

| AO <01> | Analog output<br>channels | AO GND    | Output    | Supplies the<br>voltage output of<br>the AO channels.                                                 |

| AO GND  | Analog output<br>ground   |           |           | AO GND is the<br>reference for the<br>AO channels.<br>AI GND, AO GND, D<br>GND, and<br>CHSGND are all |

| Signal                | Function                       | Reference | Direction       | Description                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------|--------------------------------|-----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       |                                |           |                 | connected<br>internally.                                                                                                                                                                                                                                                                                                                                                           |

| +5 V                  | +5 V power source              | D GND     | Output          | Provides current<br>limited +5 V power<br>output that can be<br>used to power<br>external circuitry.<br>Refer to the <b>+5 V</b><br><b>Power Source</b><br>section for more<br>information.<br>Leave this pin<br>open if you do not<br>use it.                                                                                                                                     |

| PFI<br><015>/P0.<015> | Port 0 digital I/O<br>channels | DGND      | Input or output | Digital channels<br>that can be<br>individually<br>configured as<br>input or output.<br>These channels<br>are referred to as<br>port0/line0:15 in<br>software when<br>used as digital I/O.<br>They are referred<br>to as PFI 0:15<br>when used for<br>other purposes,<br>like timing I/O.<br>Can also be<br>individually<br>configured for the<br>following uses.<br>• Digital I/O |

| Signal | Function       | Reference | Direction | Description                                                                                                                                                                                                                                                                                            |

|--------|----------------|-----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                |           |           | <ul> <li>Counter/<br/>timer input</li> <li>Counter/<br/>timer output</li> <li>External<br/>timing or<br/>trigger signal<br/>input for AI,<br/>AO, DI, DO,<br/>counter, or<br/>timers.</li> <li>Timing or<br/>trigger signal<br/>output from<br/>AI, AO, DI, DO,<br/>counter, or<br/>timers.</li> </ul> |

| D GND  | Digital ground |           |           | Supplies the<br>reference for the<br>P0.<015> pins<br>and +5 V pin.<br>AI GND, AO GND, D<br>GND, and<br>CHSGND are all<br>connected<br>internally.                                                                                                                                                     |

| CHSGND | Chassis ground |           |           | Connects directly<br>to the chassis<br>ground of the<br>USB-6451<br>enclosure. It can<br>be used as a<br>termination point<br>for shielded<br>cables to help<br>improve<br>measurement                                                                                                                 |

| Signal | Function | Reference | Direction | Description                        |

|--------|----------|-----------|-----------|------------------------------------|

|        |          |           |           | quality.                           |

| ID 1   |          |           | _         | This feature is not supported yet. |

#### **Related reference:**

• <u>+5 V Power Source</u>

# +5 V Power Source

The +5 V terminals on the I/O connector supply +5 V referenced to D GND. Use these terminals to power external circuitry.

**Notice** Never connect the +5 V power terminals to analog or digital ground or to any other voltage source on the USB-6451 or any other device. Doing so can damage the device and the computer. NI is not liable for damage resulting from such a connection.

Refer to the **USB-6451 Specifications** for more information about the USB-6451 power rating.

#### **Related information:**

• USB-6451 Specifications

# Analog Input Measurements

Learn about making analog input measurements with the USB-6451.

# Analog Input Range

Input range refers to the set of input voltages that an analog input channel can digitize with the specified accuracy. The NI-PGIA amplifies or attenuates the AI signal depending on the input range. You can individually program the input range of each AI channel on your USB-6451.

The input range affects the resolution of the USB-6451 for an AI channel. Resolution refers to the voltage of one ADC code. For example, a 20-bit ADC converts analog inputs into one of 1,048,576 possible digital values. These values are spread fairly evenly across the input range. So, for an input range of -10 V to 10 V the voltage of each code of a 20-bit ADC is:

$$\frac{10 \quad V \quad - \quad (-10 \quad V)}{2^{20}} = 19.07 \quad \mu \ V$$

The USB-6451 uses a calibration method that requires some codes to lie outside of the specified range. This calibration method improves absolute accuracy, but it increases the nominal resolution of input ranges by about 4% over what the formula shown above would indicate.

Choose an input range that matches the expected input range of your signal. A large input range can accommodate a large signal variation, but reduces the voltage resolution. Choosing a smaller input range improves the voltage resolution, but may result in the input signal going out of range.

| Input Range (V) | Nominal Resolution (µV) |

|-----------------|-------------------------|

| 10              | 19.87                   |

| 5               | 9.94                    |

| 2.5             | 4.97                    |

Table 12. USB-6451 Input Range and Nominal Resolution

| Input Range (V) | Nominal Resolution (µV) |

|-----------------|-------------------------|

| 0.2             | 0.40                    |

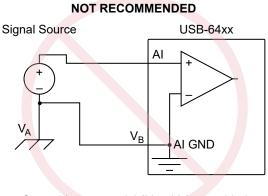

# Working Voltage Range

The NI programmable gain instrumentation amplifier (NI-PGIA) operates normally by amplifying signals of interest while rejecting common-mode signals under certain conditions.

- **Common-mode voltage (***Vcm***)**—The voltage of measurement reference potential versus AI GND. It depends on the configuration of the input terminal.

- Signal voltage (*Vs*)—The value you are trying to measure. It depends on the configuration of the input terminal.

- Total working voltage of the positive input—Equivalent to (*Vcm* + *Vs*), or subtracting AI GND from AI <0..x>+. Must be less than the maximum working range specified in the *USB-6451 Specifications*.

If any of these conditions are exceeded, the input voltage is clamped until the fault condition is removed.

| Input Terminal Configuration            | Condition                                                                                                                                                                                                                         |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Differential Mode                       | Vcm is equal to the voltage on AI <x>- vs. AI GND,<br/>where AI<x>- is the negative half of the<br/>differential pair. Refer to the <b>Differential</b><br/>Connections for Ground-Referenced<br/>Signal Sources section.</x></x> |

| Referenced Single-Ended (RSE) Mode      | Vcm is equal to 0 V since AI GND is the reference<br>for the measurement. Refer to the Non-<br>Referenced Single-Ended (NRSE)<br>Connections for Ground-Referenced<br>Signal Sources section.                                     |

| Non-referenced Single-Ended (NRSE) Mode | <i>Vcm</i> is equal to the voltage on the NR pin vs. AI GND.                                                                                                                                                                      |

Table 13. Common-Mode Voltage, Vcm

Table 14. Signal Voltage, Vs

| Input Terminal Configuration | Condition                                                                                                           |

|------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Differential Mode            | <b>Vs</b> is equal to AI <x>+ minus AI<x>-, where AI<x>- is the negative half of the differential pair.</x></x></x> |

| RSE Mode                     | <i>Vs</i> is equal to AI <x> minus AI GND.</x>                                                                      |

| NRSE Mode                    | <b>Vs</b> is equal to AI <x> minus the voltage on the NR pin.</x>                                                   |

#### **Related concepts:**

- Differential Connections for Ground-Referenced Signal Sources

- <u>Non-Referenced Single-Ended (NRSE) Connections for Ground-Referenced Signal</u>

<u>Sources</u>

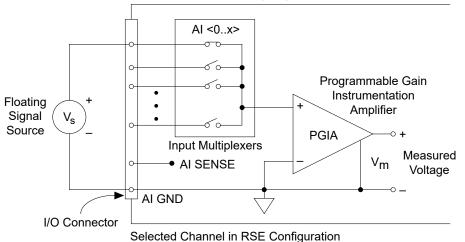

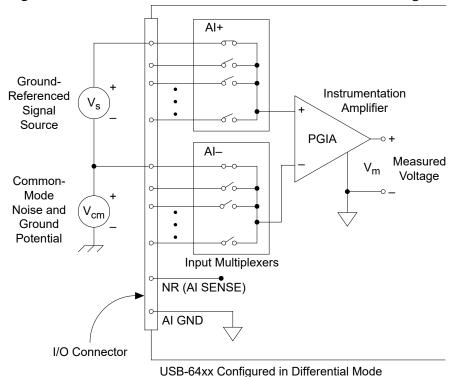

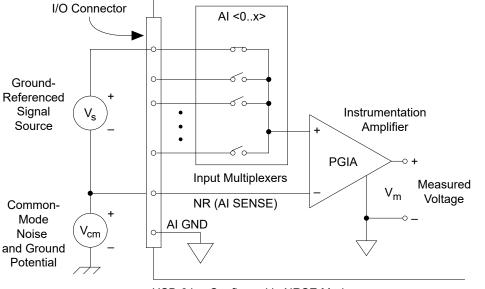

# Analog Input Terminal Configurations

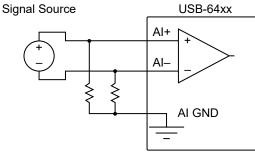

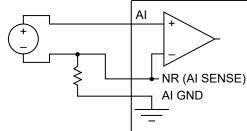

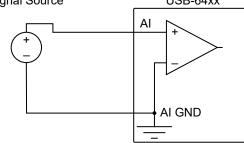

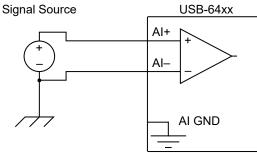

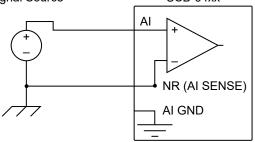

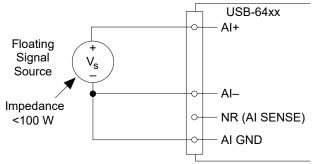

The USB-6451 supports three analog input terminal configurations: differential mode, referenced single-ended mode, and non-referenced single-ended mode.

- **Differential mode**—The USB-6451 measures the difference in voltage between two AI signals

- **Referenced single-ended (RSE) mode**—The USB-6451 measures the voltage of an AI signal relative to AI GND.

- Non-referenced single-ended (NRSE) mode—The USB-6451 measures the voltage of an AI signal relative to the NR pin (AI SENSE).

The AI terminal configuration determines the ground reference for your measurement and affects how you should connect your AI signals to the USB-6451.

Ground-reference settings are programmed on a per-channel basis. For example, you might configure the USB-6451 to scan 12 channels—four differentially-configured channels and eight single-ended channels.

The following table shows how signals are routed to the NI programmable gain instrumentation amplifier (NI-PGIA) on the USB-6451.

| Al Ground-Reference Settings | Signals Routed to the Positive<br>Input of the NI-PGIA (Vin+) | Signals Routed to the Negative<br>Input of the NI-PGIA (Vin-) |  |  |

|------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|--|--|

| RSE                          | Al <015>                                                      | AI GND                                                        |  |  |

| NRSE                         | AI <015>                                                      | NR (AI SENSE)                                                 |  |  |

| Differential                 | AI <07>                                                       | AI <815>                                                      |  |  |

Table 15. Signals Routed to the NI-PGIA on the USB-6451

**Note** You can only include a channel a single time in a given scan. When a specific channel is configured for differential mode, you cannot use the positive or negative inputs from that same channel for referenced single-ended or non-referenced single-ended measurements.

**Note** All channels must share the same measurement reference, either referenced single-ended or non-referenced single-ended, when performing single-ended measurements.

For differential measurements, AI 0 and AI 8 are the positive and negative inputs of differential analog input channel 0.

Notice The maximum input voltages rating of AI signals with respect to ground (and for signal pairs in differential mode with respect to each other) are listed in the device specifications. Exceeding the maximum input voltage of AI signals distorts the measurement results. Exceeding the maximum input voltage rating can also damage the device and the computer. NI is not liable for any damage resulting from such signal connections. AI ground-reference setting is sometimes referred to as AI terminal configuration.

#### **Related reference:**

<u>Analog Input Signal Connections</u>

## **USB-6451 Differential Mode Pairs**

• AI <0,8>

- Al <1,9>

- AI <2, 10>

- Al <3, 11>

- Al <4, 12>

- Al <5, 13>

- Al <6, 14>

- AI <7, 15>

# **Dual-Channel Scanning Considerations**

The USB-6451 can scan channel pairs at high rates and digitize the signals accurately. The USB-6451 supports dual-channel scanning in referenced single-ended (RSE) mode and non-referenced single-ended mode (NRSE) mode only.

Settling time affects accuracy in dual scanning applications. *Settling time* refers to the time it takes the NI-PGIA to amplify the input signal to the desired accuracy before it is sampled by the ADC.

When the USB-6451 switches from one AI channel to another AI channel, the USB-6451 configures the NI programmable gain instrumentation amplifier (NI-PGIA) at the same range only. The NI-PGIA then amplifies the input signal with the same gain.

The USB-6451 is designed to have fast settling times. However, several factors can increase the settling time, which decreases the accuracy of your measurements. To ensure fast settling times, do the following (in order of importance):

- 1. Use low-impedance sources.

- 2. Use short, high-quality cabling.

- 3. Carefully choose the channel scanning order.

- 4. Avoid scanning faster than necessary.

#### **Use Low-Impedance Sources**

Your signal sources should have an impedance of <1 k $\Omega$  to ensure fast settling times. Large source impedances increase the settling time of the NI-PGIA, and so decrease the accuracy at fast scanning rates. Settling times increase when scanning high-impedance signals due to a phenomenon called *charge injection*. Multiplexers contain switches, usually made of switched capacitors. When one of the channels, for example channel 0, is selected in a multiplexer, those capacitors accumulate charge. When the next channel, for example channel 1, is selected, the accumulated charge leaks backward through channel 1. If the output impedance of the source connected to channel 1 is high enough, the resulting reading of channel 1 can be partially affected by the voltage on channel 0. This effect is referred to as *ghosting*.

If your source impedance is high, you can decrease the scan rate to allow the NI-PGIA more time to settle. Another option is to use a voltage follower circuit external to the USB-6451 to decrease the impedance seen by the USB-6451.

## Use Short, High-Quality Cabling

Using short, high-quality cables can minimize several effects that degrade accuracy including crosstalk, transmission line effects, and noise.

The capacitance of the cable can also increase the settling time. NI recommends using individually shielded, twisted-pair wires that are 2 m or less to connect AI signals to the USB-6451.

## Carefully Choose the Channel Scanning Order

#### Minimize Voltage Step between Adjacent Channels

When scanning between channels that have the same input range, the settling time increases with the voltage step between the channels. If you know the expected input range of your signals, you can group signals with similar expected ranges together in your scan list. For example, group the input channel connection with closest voltage level in the same input range in pair for the scanning.

## **Avoid Scanning Faster Than Necessary**

Designing your system to scan at slower speeds gives the NI-PGIA more time to settle to a more accurate level.

#### Example 1

Averaging many AI samples can increase the accuracy of the reading by decreasing noise effects. In general, the more points you average, the more accurate the final result. However, you may choose to decrease the number of points you average and slow down the scanning rate.

Suppose you want to sample 10 channels over a period of 20 ms and average the results. You could acquire 500 points from each channel at a scan rate of 250 kS/s. Another method would be to acquire 1,000 points from each channel at a scan rate of 500 kS/s. Both methods take the same amount of time. Doubling the number of samples averaged (from 500 to 1,000) decreases the effect of noise by a factor of 1.4 (the square root of 2). However, doubling the number of samples (in this example) decreases the time the NI-PGIA has to settle from 4 µs to 2 µs. In some cases, the slower scan rate system returns more accurate results.

#### Example 2

If the time relationship between channels is not critical, you can sample from the same channel multiple times and scan less frequently. For example, suppose an application requires averaging 100 points from channel 0 and averaging 100 points from channel 1. You could alternate reading between channels—that is, read one point from channel 0, then one point from channel 1, and so on. You also could read all 100 points from channel 0 then read 100 points from channel 1. The second method switches between channels much less often and is affected much less by settling time.

# Analog Input Data Acquisition Methods

When performing analog input measurements, you either can perform software-timed or hardware-timed acquisitions.

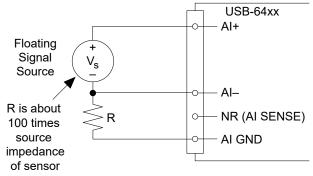

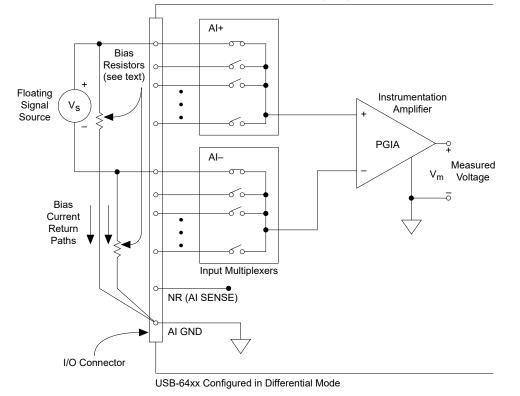

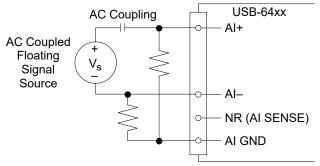

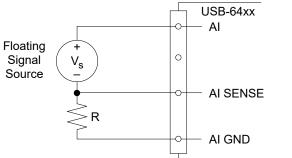

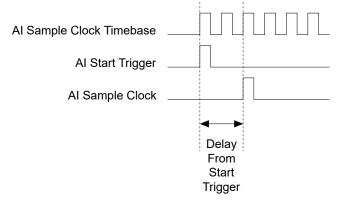

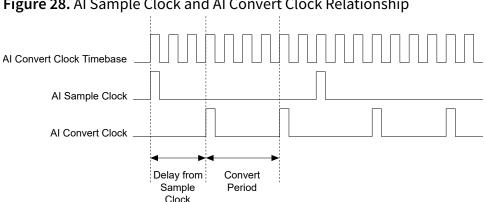

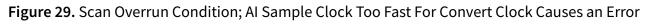

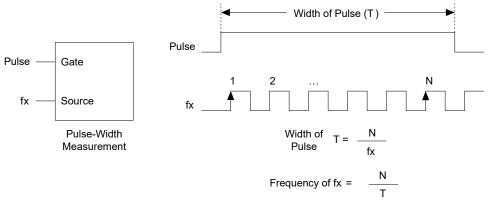

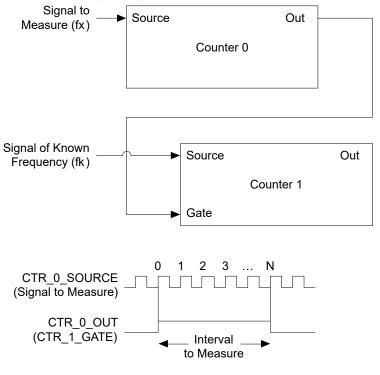

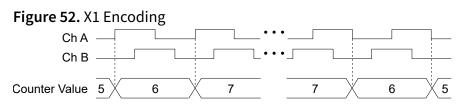

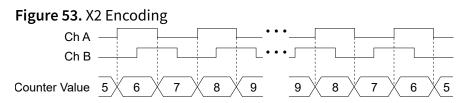

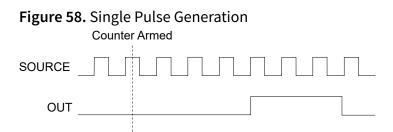

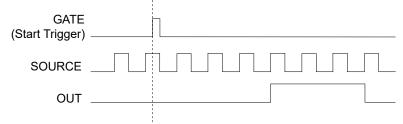

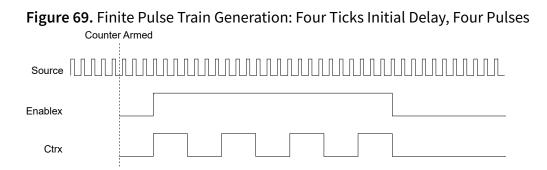

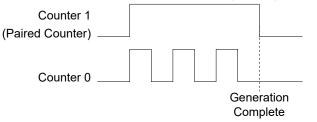

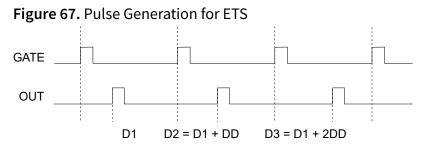

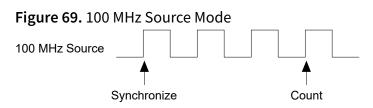

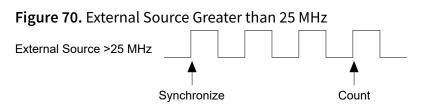

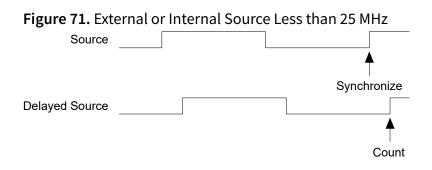

## **Software-Timed Acquisitions**